## Differential Trace Design Rules Truth vs Fiction

There is no shortage of design rules available when people talk about differential traces on circuit boards. At various times you can hear people argue that there is a need for, or there is no need for, a variety of special rules. In general, the rules fall into one or more of these five categories:

- Planes: There must be a continuous power system plane underneath the differential pair.

- Length: Care must be taken to ensure that differential traces are of equal length.

- Spacing 1: Care must be taken to place the traces as close together as possible.

- Spacing 2: Care must be taken to ensure that the spacing between traces is constant everywhere along the length of the traces.

- Impedance: Differential impedance rules must be applied.

So let's set the record straight about these rules right now. ***NONE*** of them are inherently required by the fact that we are using differential signals! There is nothing about differential signals that necessitates any of these rules in any ordinary design.

But some of them *might* be required if we are worried about signal integrity issues in our designs. So let's start with the assumption that we DO care about signal integrity. Otherwise, there is nothing more to talk about! Agreeing on that, let's look at these individual rules from the standpoint of various signal integrity issues and see when, if ever, they need be applied.

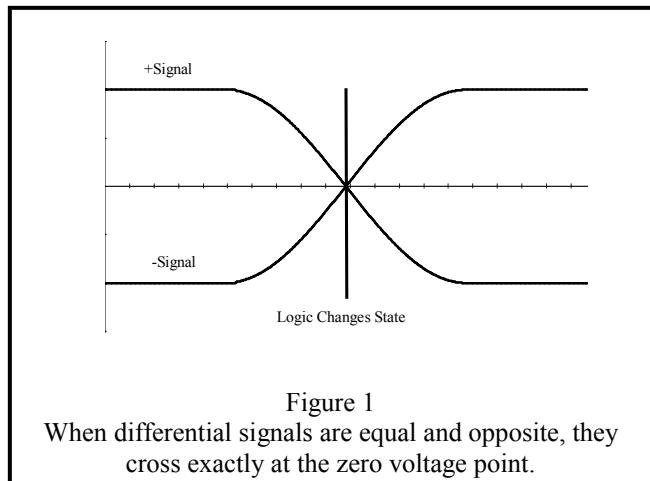

**Equal length/continuous planes rules:** People will argue that traces do not need to be equal length because the timing budgets of differential devices are really quite wide. So, substantially different trace lengths can be allowed and still fall within the timing budget. People will also argue that a return path is not needed since by definition the differential signals are equal and opposite. What travels down one trace of the differential pair returns on the other trace. There is no current returning on any other path, specifically the power system planes, so ground return continuity is not an issue.

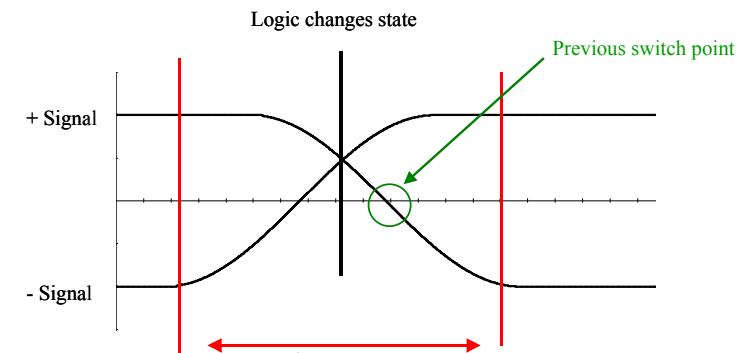

Both of these statements are correct. *But they cannot both be correct at the same time!* If the traces are not the same length (and assuming we have true differential driver), then the signals *cannot* meet the equal and opposite assumption at the receiver. Figures 1 and 2 show why. If the signals are not equal and opposite at the receiver, then *somewhere* there will be a return current (the difference between the two signals on the traces). If there is no provision for this current on power system planes underneath the traces, then the path(s) of the return current will be undefined, and the return signal might well cause an EMI or noise problem on the board.<sup>1</sup>

## Differential Trace Design Rules Truth vs Fiction

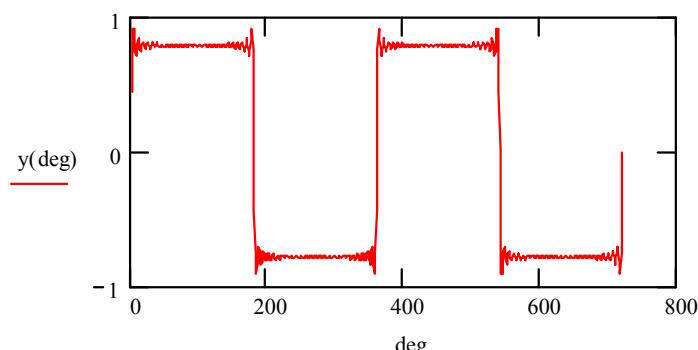

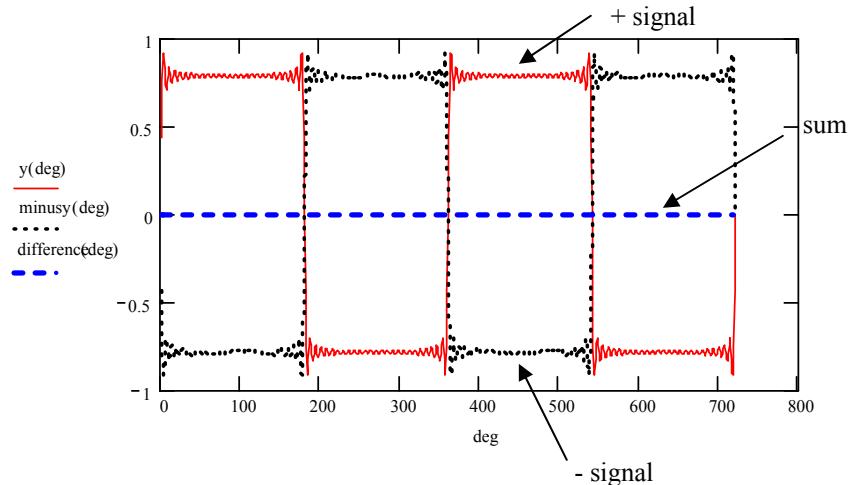

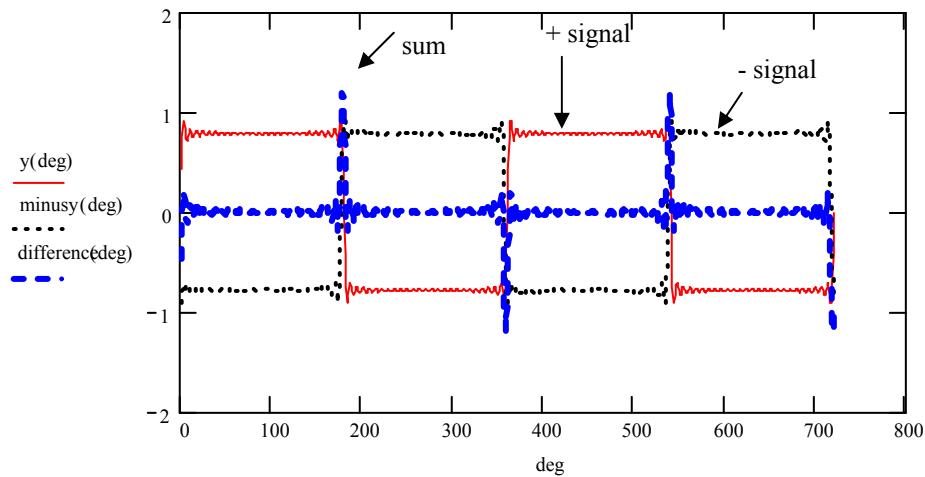

**Equal length rules, part 2:** The square wave in Figure 3 has been generated in MathCad using a Fourier series estimation technique. In a differential signal pair, we might have this signal on one trace, and the opposite signal on another trace. These two signals would then sum to zero at the receiver (see Figure 4). Now consider what happens when we let one trace be *slightly* longer than the other trace. This is the same thing as the two signals (the positive and negative signals) being slightly out of phase at the receiving end. The signal on the shorter trace would arrive slightly earlier than would the one on the longer trace. Figure 5 illustrates the resulting *difference* signal when this happens. Figure 6 illustrates just this difference signal, showing more clearly that it can be *very* pronounced and also of considerable magnitude for just a *very* minor difference in phase. The “noise” pulse width is equal to the phase shift between the two signals.

Figure 2

The (-) trace is shorter than in Figure 1, and it is no longer true that the differential signals are equal and opposite over the range indicated by the arrow. Thus, there will be current flowing through the power system during this time frame.

*This difference* signal might now be showing up on the ground plane. Not only is it *not* consistent with our assumption that there are no currents on the ground plane, the current that now shows up on the plane has sharp rise times, is of considerable magnitude, and can be a serious EMI problem!

An interesting question is, “What kind of dimensions are we looking at here before this becomes a problem?” Part of the answer depends on the rise time of the signal. But for even a poorly defined square wave, a one- or two-degree phase shift could be significant.

Assume we have a 50 MHz square wave. That means there are  $100 * 10^6$  half-cycles in one second, or there is a single half-cycle every 10 nanoseconds. If a half-cycle occurs in 180 degrees

Figure 3

A square wave generated using a Fourier Series in MathCad.

## Differential Trace Design Rules Truth vs Fiction

Figure 4

The square wave is on one trace and its exact inverse is on the return trace. They combine to zero.

Figure 5

If one trace in the differential pair is a slightly different length than the other, a noise signal will be present when they change states.

## Differential Trace Design Rules Truth vs Fiction

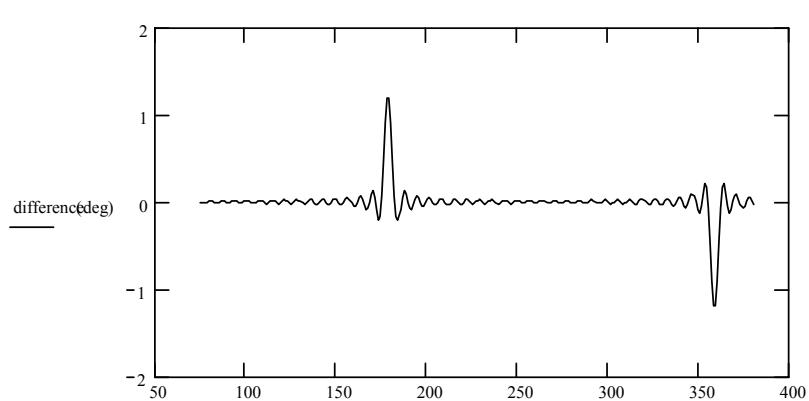

Figure 6

A closer look at the noise signal from Figure 5

(half of a 360 degree complete cycle), and if propagation time is 6" per nanosecond in FR4, then one degree phase shift equates to 333 mils distance. If we set one degree as our threshold, (which might be too much!) then the corresponding offsets would be:

| Frequency (MHz) | Offset (mils, or thousandth in.) |

|-----------------|----------------------------------|

| 50              | 333                              |

| 500             | 33                               |

| 5 GHz           | 3                                |

**Conclusion:** The equal length design rule is important *IF* the signal equal-and-opposite assumption is important. The signal equal-and-opposite assumption is important if we are worried about EMI or if we require discontinuities in the power system grounds between two circuits.

**Close together rule, part 1:** It is generally understood that EMI is related to loop area.<sup>2</sup> The loop area is defined as the area between the signal path and its return path. On differential traces, the signal is on one trace and the return is on the other trace. So the loop area is a function of how close the traces are routed together.

If we are concerned about EMI, we must route the traces close together. The more closely we route them to each other, the smaller the loop area will be and the less EMI that will be generated.

**Close together rule, part 2:** One of the primary advantages of differential signals is the signal-to-noise ratio improvement that is obtained. Since the signal is one polarity on one trace and the other polarity on the other trace, the resulting signal at the receiving device is twice what the single-ended signal would be.

An additional advantage is that the receiving circuits are designed so that they are highly sensitive to the difference in signal level between the two traces, but highly insensitive to shifts in signal level that occur on both traces. This is normally called common mode rejection at the receiving device.

## Differential Trace Design Rules Truth vs Fiction

---

In order to have good common mode noise rejection, it is important that any noise that is present affects the signals on both traces equally. That is, if noise is coupled into one trace, an equal amount of noise must be coupled into the other trace. Then the common mode rejection capability of the receiving circuit will reject the noise. But if noise is coupled into one trace more strongly than into the other trace, the noise will appear as a differential mode signal to the receiver and be amplified.

The way to ensure that any noise is coupled equally into both traces is to route the two traces very close together. Then they will both be in the same noise environment.

**Conclusion:** The close together rule is important *IF* we are worried about EMI or *IF* we are worried about common mode rejection of noise that has been coupled into our traces.

**Continuous plane rule, part 2:** Assuming signal integrity issues are important, we are probably worried about signal reflections at the end of traces. If we are worried about reflections, then we need impedance controlled traces. If we need impedance controlled traces, then it is almost axiomatic that we need continuous planes underneath those traces.<sup>3</sup> Otherwise, impedance control is very difficult to achieve and impedance discontinuities will develop.

**Constant spacing rule:** When two traces are routed close together, there is coupling between them. Ordinarily we call that crosstalk. But in the very special case of differential signals, we don't refer to it as crosstalk, and there is no negative implication to this coupling. The very special case derives from the fact that the two differential signals (in an ordinary case referred to as the aggressor and the victim signals) are *perfectly* correlated. One is the exact inverse of the other.

There is a *consequence* of this coupling. The consequence is that the resulting impedance of the trace reduces from its single-ended value.<sup>4</sup> The normal expression for the resulting impedance is

$$Z = Z_0 - Z_{12}$$

where  $Z_{12}$  represents the effects of the coupling.

The coupling is a function of the spacing. Traces spaced very far apart have little or no effective coupling, and their characteristic impedance is simply  $Z_0$ . Traces placed very close together have some degree of coupling, and therefore lower impedance. If we are concerned about using impedance controlled traces, then we are also concerned about having a constant impedance everywhere along the trace. Otherwise, the resulting impedance discontinuities may cause reflections.

**Conclusion:** If we are using controlled impedance traces, then it is important that the separation between traces remain *constant* everywhere along their length. (Note that this conclusion says nothing about *how closely* they should be spaced. *That* conclusion derives from EMI and common mode noise rejection considerations.)

**Differential impedance rule:** The so-called differential impedance rule simply says we must calculate a differential impedance for proper trace termination if differential signals are routed close together. There is nothing magical about differential impedance. We would not have to use differential impedance calculations if traces were routed widely apart. But:

## Differential Trace Design Rules Truth vs Fiction

---

IF signal reflections are an issue, so that we need impedance controlled traces, and

IF the traces need to be routed close together for EMI and/or common mode rejection reasons,

THEN the *consequence* is that differential calculations become necessary.

**Summary:** There is nothing about differential signals that requires special routing rules unless we are concerned about signal integrity issues. Then, certain signal integrity issues result in certain design guidelines. Some of these guidelines have *consequences* that lead to additional design rules that might not have been necessary otherwise.

---

Footnotes:

1. For a discussion of planes and problems associated with plane discontinuities, see Brooks, "Splitting Planes for Speed and Power," available from <http://www.ultracad.com>.

2. See Brooks, "Loop Areas, Close 'Em Tight," Printed Circuit Design Magazine, January, 1999, available from <http://www.ultracad.com>.

3. There are a variety of articles and publications regarding trace impedance guidelines. For example see "PCB Impedance Control: Formulas and Resources," March, 1998, "Impedance Terminations: What's the Value?" March, 1999; and "What Is Characteristic Impedance?" by Eric Bogatin, January, 2000, p. 18, all from Printed Circuit Design Magazine. For embedded microstrip formulas see "Embedded Microstrip," Printed Circuit Design, February, 2000. All articles (except Bogatin's) are reprinted on UltraCAD's web site.

4. See Brooks, "Differential Impedance, What's the Difference?" Printed Circuit Design Magazine, August, 1998, available from <http://www.ultracad.com>,

---

About the author:

**Douglas Brooks** has a B.S and an M.S in Electrical Engineering from Stanford University and a PhD from the University of Washington. During his career has held positions in engineering, marketing, and general management with such companies as Hughes Aircraft, Texas Instruments and ELDEC.

Brooks has owned his own manufacturing company and he formed UltraCAD Design Inc. in 1992. UltraCAD is a service bureau in Bellevue, WA, that specializes in large, complex, high-density, high-speed designs, primarily in the video and data processing industries. Brooks has written numerous articles through the years, including articles and a column for Printed Circuit Design Magazine, and has been a frequent seminar leader at PCB Design Conferences. His primary objective in his speaking and writing has been to make complex issues easily understandable to those without a technical background. You can visit his web page at <http://www.ultracad.com> and e-mail him at [doug@ultracad.com](mailto:doug@ultracad.com).