# CARACTERISTIQUES ELECTRIQUES DES DIFFERENTES TECHNOLOGIES DE CIRCUITS INTEGRÉS LOGIQUES

## A- TECHNOLOGIE «TTL»: (Transistor Transistor Logic)

1°- Tension d'alimentation:  $V_{AL} = 5V \pm 5\%$  avec  $I_{AL} = 22 \text{ mA}$  pour une porte logique simple.

### 2°- Rapports entre tensions et niveaux logiques:

- a- En entrée:  $0V < V_E < 0,8V \Rightarrow E = 0$

$2V < V_E < 5V \Rightarrow E = 1$

$0,8V < V_E < 2V \Rightarrow \text{Zone interdite}$

- b- En sortie:  $0V < V_s < 0,4V \Rightarrow S = 0$

$2,4V < V_s < 5V \Rightarrow S = 1$

$0,4V < V_s < 2,4V \Rightarrow \text{Zone interdite}$

### 3°- Rapports entre courants d'entrée et niveaux logiques:

- a- Au niveau logique 1:  $I_E = OA \Rightarrow$  une entrée en l'air est au niveau logique 1.

- b- Au niveau logique 0:  $I_E > 1,6 \text{ mA}$  avec  $I_E$  courant sortant.

Lorsqu'une résistance doit être placée entre une entrée d'opérateur TTL et la masse, sa valeur ne doit pas excéder:

$$R_E \text{ max} = V_E \text{ max} / I_E \text{ min} \quad \text{soit } 500 \Omega.$$

### 4°- Intensités de courant de sortie maximales:

- a- Au niveau logique 1:  $I_{Smax} = 0,4 \text{ mA}$  (courant sortant)

- b- Au niveau logique 0:  $I_{Smax} = 16 \text{ mA}$  (courant rentrant).

5°- Sortance: C'est le nombre d'entrées de circuits intégrés de la même technologie que l'on peut relier à la même sortie.

$$n = 16 \text{ mA} / 1,6 \text{ mA} = 10 \Rightarrow n = 10$$

## 6°- Fréquence maximale de fonctionnement:

Pour une porte logique simple: on relève  $t_{PLH} = 22\text{ns}$  et  $t_{PHL} = 15\text{ns}$

soit une période minimale de  $T = t_{PLH} + t_{PHL} = 37\text{ ns}$

et une fréquence maximale de  $f = 1 / T \approx 27\text{ MHz}$

## B- TECHNOLOGIES DERIVEES DE LA TECHNOLOGIE «TTL»:

|                          | S (Schottky) | LS (Low Sch.) | HCT (High speed) |     |

|--------------------------|--------------|---------------|------------------|-----|

| $V_{E_{max}}\text{ NL0}$ | 0,8          | 0,8           | 0,8              | V   |

| $V_{E_{min}}\text{ NL1}$ | 2            | 2             | 2                | V   |

| $V_{S_{max}}\text{ NL0}$ | 0,5          | 0,5           | 0,33             | V   |

| $V_{S_{min}}\text{ NL1}$ | 2,7          | 2,7           | 3.84             | V   |

| $I_{E_{min}}\text{ NL0}$ | 2            | 0,4           | # 0              | mA  |

| $I_{S_{max}}\text{ NL1}$ | 1            | 0,4           | 4.8              | mA  |

| $I_{S_{max}}\text{ NL0}$ | 20           | 8             | 4.8              | mA  |

| Sortance                 | 10           | 20            | infinie          |     |

| $t_{PLH}$                | 7            | 15            | 23               | ns  |

| $t_{PHL}$                | 8            | 15            | 23               | ns  |

| $T_{min}$                | 15           | 30            | 46               | ns  |

| $f_{max}$                | 66           | 33            | 21               | MHz |

| $I_{AL}$                 | 36           | 4.4           | 0.4              | mA  |

A la lecture de ce tableau, on constate que les différences essentielles entre les technologies TTL, S et LS, résident au niveau de la consommation en énergie électrique, et par voie de conséquence au niveau de la rapidité: plus un circuit consomme de l'énergie électrique, plus il est rapide.

Il faut noter que la série 74 HCT est, contrairement aux apparences, de technologie CMOS compatible TTL et dérivées, et non pas dérivée de la TTL.

1°- Tensions d'alimentation:  $3 \text{ V} < V_{\text{AL}} < 15 \text{ V}$

sauf circuits à alimentation fixe 5V.

avec  $I_{\text{AL}} = 0.25 \text{ mA}$  pour une porte logique simple.

2°- Rapports entre tensions et niveaux logiques:

a- En entrée:  $0 < V_E < V_{\text{AL}}/2 \Rightarrow E = 0$

$V_{\text{AL}}/2 < V_E < V_{\text{AL}} \Rightarrow E = 1$

b- En sortie:  $S = 0 \Rightarrow V_S = 0 \text{ V}$

$S = 1 \Rightarrow V_S = V_{\text{AL}}$ .

3°- Courants d'entrée: dans tous les cas  $I_E = 0 \text{ A}$ .

4°- Modèle de sortie des opérateurs CMOS:

a- Au niveau logique 0: Modèle de Thévenin:  $V_{\text{TH0}} = 0 \text{ V}$

b- Au niveau logique 1: Modèle de Thévenin:  $V_{\text{TH1}} = V_{\text{AL}}$

5°- Sortance: En théorie elle est infinie, mais en pratique on la limite à 50.

6°- Fréquence maximale de fonctionnement:

Pour une porte logique simple: on relève  $t_{\text{PLH}} = 250 \text{ ns}$  et  $t_{\text{PHL}} = 250 \text{ ns}$

soit une période minimale de  $T = t_{\text{PLH}} + t_{\text{PHL}} = 500 \text{ ns}$

et une fréquence maximale de  $f = 1 / T \approx 2 \text{ MHz}$

## D-COMPATIBILITE DES PRINCIPALES TECHNOLOGIES:

Les 4 principales technologies utilisées sont: la TTL, la TTL-LS, la CMOS HCT et la CMOS série 4000 et la CMOS série 74HCT; le tableau ci-dessous indique les cas de compatibilité de ces technologies entre-elles:

| vers<br>de | TTL                | TTL-LS             | 4000               | HCT |

|------------|--------------------|--------------------|--------------------|-----|

| TTL        | oui <sub>(1)</sub> | oui <sub>(2)</sub> | NON <sub>(3)</sub> | oui |

| TTL-LS     | oui <sub>(4)</sub> | oui <sub>(1)</sub> | oui                | oui |

| 4000       | NON <sub>(5)</sub> | oui <sub>(6)</sub> | oui                | oui |

| HCT        | oui <sub>(7)</sub> | oui <sub>(8)</sub> | oui                | oui |

- (1) Avec limites par la valeur de sortance.

- (2) Avec sortance équivalente de  $Ismax_{TTL} / Iemin_{LS} = 16mA / 0.4mA = 40$

- (3) Incompatibilité entre les tensions de sortie TTL et les tensions d'entrée CMOS

- (4) Avec sortance équivalente de  $Ismax_{LS} / Iemin_{TTL} = 8mA / 1.6mA = 5$

- (5) Incompatibilité entre courant de sortie CMOS et courant d'entrée TTL.

- (6) Limitée à 2 entrées LS de préférence.

- (7) Avec sortance équivalente de  $Ismax_{HCT} / Iemin_{TTL} = 4.8mA / 1.6mA = 3$

- (8) Avec sortance équivalente de  $Ismax_{HCT} / Iemin_{LS} = 4.8mA / 0.4 = 12$

#### E- PROBLEMES LIES A L'UTILISATION DE LA TECHNOLOGIE CMOS 4000:

Contrairement à la technologie TTL, une entrée d'opérateurs CMOS ne peut en aucun cas se trouver «en l'air». Elle doit obligatoirement être «rappelée» à une tension.

##### 1°- Résistance de rappel à $+V_{AL}$ :

Quand le niveau d'entrée fixé par un organe à contact est le niveau 0, le niveau 1 est rappelé par la résistance:

$$V_E = V_{AL} - R \cdot I_E = V_{AL} \quad \Rightarrow \quad E = 1$$

## 2°- Résistance de rappel à OV:

Quand le niveau d'entrée fixé par un organe à contact est le niveau 1, le niveau 0 est rappelé par la résistance:

$$V_E = R \cdot I_E = OV \Rightarrow E = 0$$

## F- CIRCUITS INTEGRES PERMETTANT DE REALISER UN INTERFACE ENTRE TTL ET CMOS:

Afin de ne pas avoir de problème de compatibilité entre TTL et CMOS4000, on place entre ces circuits des AMPLIFICATEURS LOGIQUES, (ou Buffers).

Ces circuits admettent des tensions d'entrée élevées, notamment supérieures à la tension d'alimentation, et fournissent en sortie des états logiques correspondant strictement aux tensions d'alimentation; d'autre part ils peuvent fournir des intensités de courant en sortie supérieures à celles en vigueur dans la même technologie.

Ces amplificateurs logiques peuvent être, d'un point de vue fonction logique, soit des opérateurs OUI, soit des opérateurs NON.

Exemples de références:

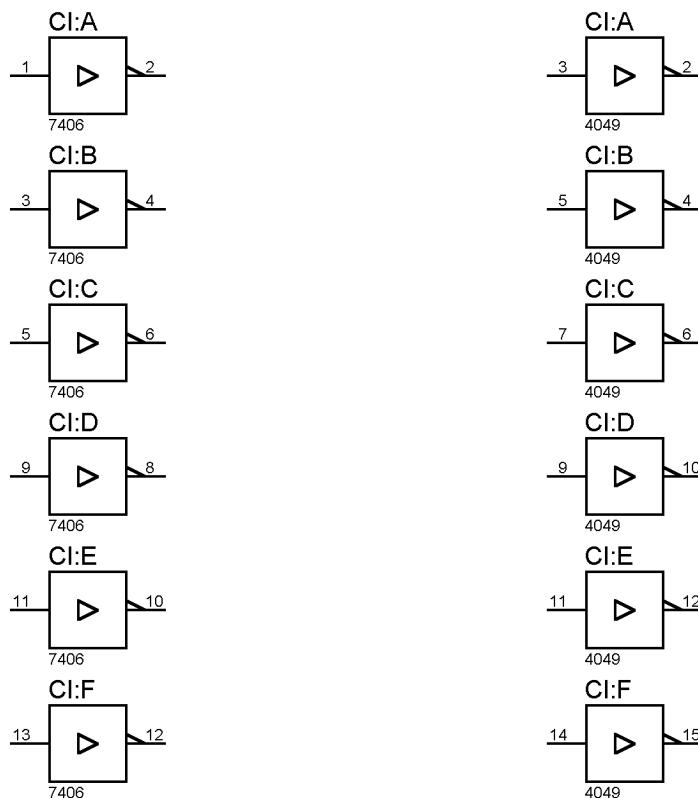

\* en technologie TTL: 7406, 7407, ...

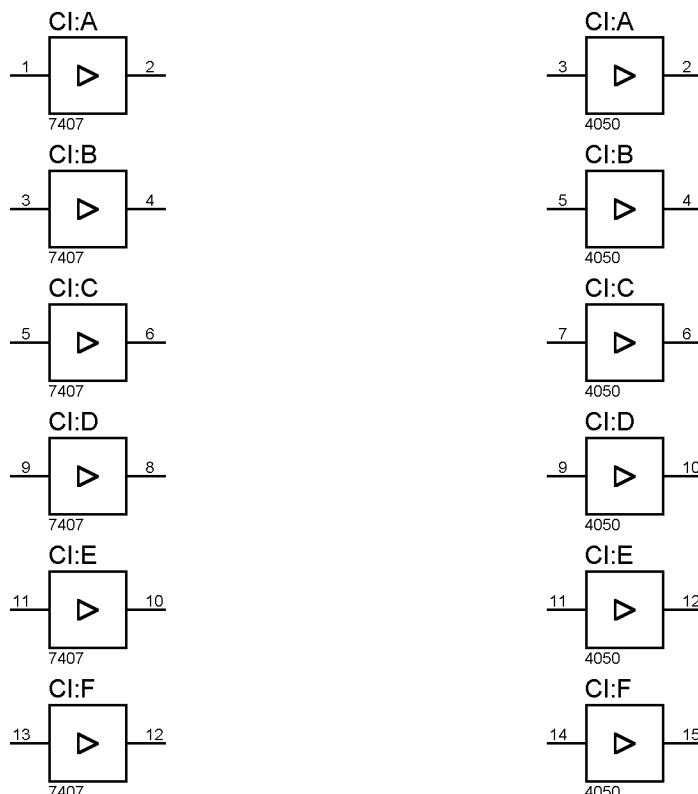

\* en technologie CMOS: 4049, 4050, ...

## AMPLIFICATEURS LOGIQUES INVERSEURS:

## AMPLIFICATEURS LOGIQUES NON-INVERSEURS:

|                     |                                               |               |

|---------------------|-----------------------------------------------|---------------|

| Elaboré à l'aide de | LP La Chauvinière - NANTES -                  | Electronique  |

| PROTEUS             | Interface CMOS/TTL<br>Amplificateurs logiques | 17/12/02      |

| Isis-5.1            |                                               | Version n°: 1 |

| 1/1                 |                                               | RIVALIN G.    |