# Possibility of Transport Through a Single Acceptor in a Gate-All-Around Silicon Nanowire PMOSFET

Byoung Hak Hong, Young Chai Jung, Jae Sung Rieh, *Senior Member, IEEE*, Sung Woo Hwang, *Member, IEEE*, Keun Hwi Cho, *Member, IEEE*, K. H. Yeo, S. D. Suk, Y. Y. Yeoh, M. Li, Dong-Won Kim, Donggun Park, *Fellow, IEEE*, Kyung Seok Oh, and Won-Seong Lee

**Abstract**—Temperature-dependent electrical transport measurements of cylindrical shaped gate-all-around silicon nanowire p-channel MOSFET were performed. At 4.2 K, they show current oscillations, which can be analyzed by single hole tunneling originated from nanowire quantum dots. In addition to this single hole tunneling, one device exhibited strong current peaks, surviving even at room temperature. The separations between these current peaks corresponded to the energy of 25 and 26 meV. These values were consistent with the sum of the bound-state energy spacing and the charging energy of a single boron atom. The radius calculated from the obtained single-atom charging energy was also comparable to the light-hole Bohr radius.

**Index Terms**—Gate-all-around (GAA), silicon nanowire FET (SNWFET), single-acceptor atom, temperature dependence.

## I. INTRODUCTION

Rapid scaling of MOSFETs has led us into a regime where counting individual dopants (donors and acceptors) [1]–[3] as well as individual oxide charges [4] is important in determining the threshold voltage of each device. The threshold voltage is not the quantity determined from the average doping density any more, and there is an appreciable device-to-device fluctuation due to irregular distribution of individual dopants. As the device size becomes even smaller, we encounter a device whose characteristic is determined completely by the existence of a single impurity in the channel. Recently, various transport studies regarding such single-dopant effects have been

Manuscript received July 23, 2008; revised February 19, 2009 and April 9, 2009. First published May 2, 2009; current version published November 11, 2009. This work was supported by the Korean Ministry of Science and Technology through the Creative Research Initiatives Program Research Center for Time Domain Nano-Functional Devices (TiNa) of the Ministry of Science and Technology (MOST)/Korea Science and Engineering Foundation (KOSEF) under Contract R16-2007-007-01001-0(2008). The work of B. H. Hong, Y. C. Jung, S. W. Hwang, and J. S. Rieh was supported by the second stage of Brain Korea 21 Project in 2008. The work of S. W. Hwang was supported by Korea University. This paper was presented in part at the IEEE Silicon Nanoelectronics Workshop, HI, June 2008. The review of this paper was arranged by Associate Editor T. Hiramoto.

B. H. Hong, Y. C. Jung, and S. W. Hwang are with the Research Center for Time Domain Nano-Functional Devices (TiNa) and the School of Electrical Engineering, Korea University, Seoul 136-701, Korea (e-mail: bhhong@korea.ac.kr; fxying@korea.ac.kr; swhwang@korea.ac.kr).

J. S. Rieh is with the School of Electrical Engineering, Korea University, Seoul 136-701, Korea (e-mail: jsrieh@korea.ac.kr).

K. H. Cho, K. H. Yeo, S. D. Suk, Y. Y. Yeoh, M. Li, D.-W. Kim, D. Park, K. S. Oh, and W.-S. Lee are with the Advanced Technology Development Team 1, R&D Center, Samsung Electronics Comapny, Yongin 446-711, Korea (e-mail: keunhwi.cho@samsung.com; dongwon.kim@samsung.com; donggun.park@samsung.com; oks.oh@samsung.com; wonseong.lee@samsung.com).

Color versions of one or more of the figures in this paper are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/TNANO.2009.2021844

reported [5]–[8]. In the case of nanowire devices, a single impurity in the channel will also strongly affect the characteristics of the whole device because the impurity, no matter where it exists in the length direction, can easily influence the entire current flow.

Gate-all-around (GAA) silicon nanowire FET (SNWFET) is considered as an ideal candidate among the devices with 3-D electric field control [9]. Previously, we reported the characteristics of twin SNWFETs fabricated by using full CMOS processes [10]. Low-temperature ( $T$ ) characterization of these devices exhibited interesting single-electron tunneling [11] and shell filling behaviors [12]. However, so far, the effect of single dopant on these GAA structure has rarely been reported. In this paper, we report the evidence of single-impurity dominant transport in a GAA SNW PMOS (p-channel MOS) FET fabricated by similar CMOS processes. We performed systematic  $T$ -dependence studies of the transport characteristics, and we observed anomalous current peaks from one of the devices. We analyzed these peaks in terms of the evidence of transport through single-acceptor states.

## II. DEVICE FABRICATIONS

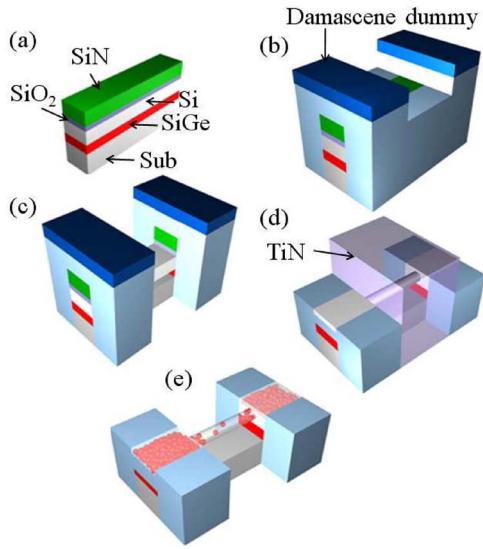

Fig. 1 shows the detailed fabrication procedures of our GAA SNW PMOSFETs [10]. The description of the processes is also summarized in the figure. A cylindrical SNW with the radius ( $r$ ) of 5 nm and the length ( $L$ ) of 60 nm is bridging the source and the drain contacts, and it is fully surrounded by a 3.5-nm  $\text{SiO}_2$  and a TiN gate. The  $\text{H}_2$  trimming after the etching of the sacrificial SiGe layer results in circular cross sections with smooth surface [10]. The penetration of the implanted dopants during the postimplantation heat treatments creates p regions on both ends of the SNW. The discrete dopants that can become the source of the single-dopant transport are the residual boron atoms diffused further into the middle of the channel from this p region [see Fig. 1(e)]. Our nanowire is only unintentionally doped during the epitaxy, and the average concentration of the impurities introduced during epitaxy is expected to be much smaller than the concentration of the outdiffused dopants. Therefore, the chance for the impurities originated from the epitaxial growth to participate in the transport can be negligible.

## III. RESULTS AND DISCUSSIONS

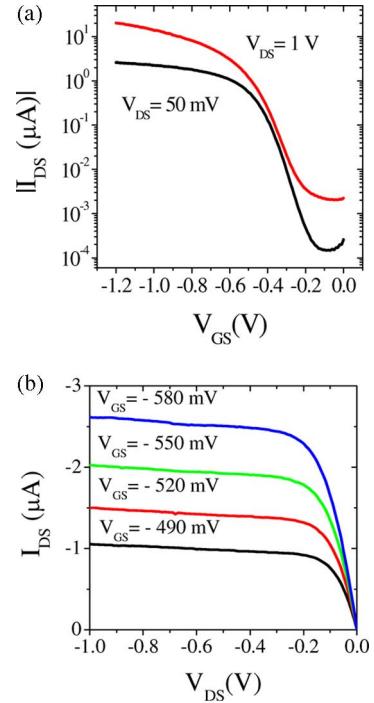

Fig. 2(a) and (b) shows a typical room temperature  $T$ , drain current–gate voltage ( $I_{DS}$ – $V_{GS}$ , in log scale) and drain

Fig. 1. Fabrication procedures of our GAA SNW PMOSFET. (a) Epitaxial growth of sacrificial SiGe and active silicon layer, SiN hard mask deposition and trimming, etching for shallow trench isolation. (b) Trench oxide fill, Damascene dummy deposition, and Damascene process for SiN hard mask opening. (c) Field oxide recess and removal of SiGe layer. (d)  $H_2$  annealing for trimming of SNW, gate oxidation, TiN gate filling, blocking layer formation, and ion implantation. (e) Schematic dopant distribution in the SNW.

current–drain voltage ( $I_{DS}$ – $V_{DS}$ , in linear scale) characteristic, respectively, measured from one of the SNW PMOSFETs. The drain-induced barrier lowering, subthreshold swing, and ON–OFF current ratio from these characteristics are 27.3 mV/V, 73 mV/decade, and more than  $10^4$ , respectively. As shown in Fig. 2(b), there are no kinks in the saturation region, which indicates that the channel of the nanowire is fully depleted [13].

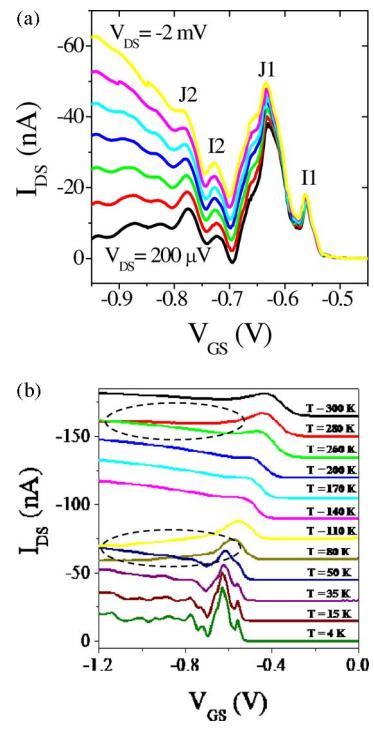

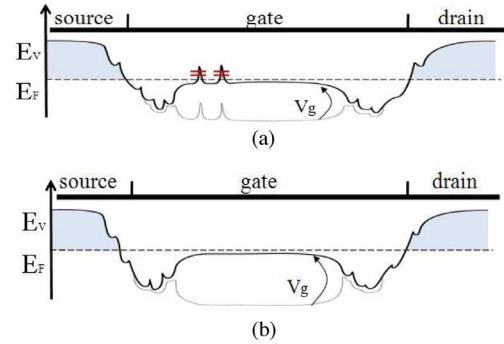

We obtained the low- $T$  characteristics of several SNW PMOSFETs fabricated in the same batch. At low  $T$ , we usually observe regular current oscillations, which are originated from single hole tunneling of the quantum dot defined by the gate-bias-induced band bending of the p source/lightly doped nanowire/p drain [12], [14], [15] [also see the band diagram of Fig. 5(b)]. Fig. 3(a) shows the  $I_{DS}$ – $V_{GS}$  measured from one device (device A) at  $T = 4.2$  K. This device exhibits unexpected behaviors. Near the turn-ON region of the device ( $-0.8 < V_{GS} < -0.5$  V), it exhibits strong current peaks whose shapes are almost triangular. Their shape is different from other regular Coulomb oscillation peaks in the region  $V_{GS} < -0.8$  V. The shapes of the first and the second peak (denoted by I1 and J1) are almost independent of the value of  $V_{DS}$ . Fig. 3(b) shows the  $T$ -dependence of these anomalous current peaks at low  $V_{DS}$  ( $-500$   $\mu$ V). The current peaks are merged into a single large peak at  $T = 50$  K, and it persists even at room  $T$ . The circled regions at  $T = 80, 110$ , and  $280$  K show the slopes that are different from those of other  $T$ 's. They could be originated from oxide charge instabilities. However, they do not affect the peak structures that are the main focus of this paper.

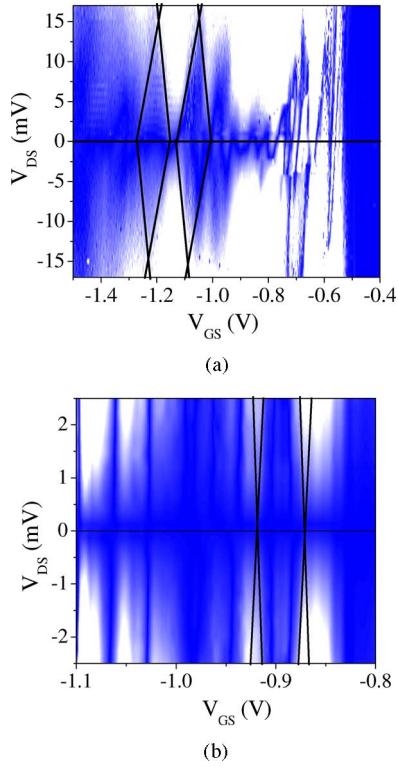

Fig. 4(a) shows the 4.2 K contour plots of  $dI_{DS}/dV_{DS}$  in the  $V_{DS}$ – $V_{GS}$  planes measured from device A with anomalous peaks. Fig. 4(b) shows the 4.2 K contour plots of  $dI_{DS}/dV_{GS}$

Fig. 2. (a)  $I_{DS}$ – $V_{GS}$  (log scale) and (b)  $I_{DS}$ – $V_{DS}$  (linear scale) characteristics of a typical SNW PMOSFET measured at room temperature. They show clear PMOS behavior with reasonable subthreshold swing and ON–OFF ratio.

Fig. 3. (a)  $I_{DS}$ – $V_{GS}$  at various  $V_{DS}$  values measured from one of our SNW PMOSFETs (device A). Data were taken at  $T = 4.2$  K. Four anomalous peaks are observed (denoted as I1, I2, J1, and J2). (b)  $I_{DS}$ – $V_{GS}$  measured from the same device at several different  $T$ s.  $V_{DS} = 500$   $\mu$ V. The current peak structure survives even at  $T = 300$  K.

Fig. 4.  $V_{GS}$ – $V_{DS}$  contour plots of  $dI_{DS}/dV_{DS}$  measured at 4.2 K. (a) Device A. (b) Device B. The solid lines denote the single hole tunneling Coulomb diamond from which the capacitance values are extracted.

in the  $V_{DS}$ – $V_{GS}$  planes measured from a normal device (device B). Device B of Fig. 4(b) shows clear Coulomb diamonds that are symmetric against the  $V_{DS}$  axis, and it also shows almost periodic oscillations in  $V_{GS}$ . However, the diamonds of device A of Fig. 4(a) are strongly asymmetric and the period of the oscillations is irregular, especially in the range  $-0.8 \text{ V} < V_{GS} < -0.6 \text{ V}$ .

We interpret the strong asymmetric peak of device A as the evidence of transport through single-acceptor impurities in the channel. Assuming the diffusion of semi-infinite solid and using the doping concentration in the center of the nanowire ( $L/2$ ), the average number of impurities ( $N$ ) in the nanowire channel is estimated by the following formula:

$$N = \pi r^2 (L - 30 \text{ nm}) C_s \left[ 1 - \text{erf} \left( \frac{L}{4\sqrt{Dt}} \right) \right]$$

where  $C_s$ ,  $D$ , and  $t$  are the doping concentration of the implanted source/drain region, diffusion constant, and total time of diffusion, respectively. Here, we use the penetration depth (the length of the p region in the SNW) of 15 nm [12]. The total heat budget after boron ion implantation of the source and the drain region is 800 °C for  $t = 10$  min. It is difficult to exactly know the value of  $C_s$ , and we assume the worst case of  $10^{19} \text{ cm}^{-3}$ . With the  $D$  value of  $\sim 10^{-15} \text{ cm}^2/\text{s}$  (at 800 °C),  $N \approx 0.25$ . The estimated number of diffused dopants in the channel is consistent with the fact that the anomalous peaks occur only in one device. We analyze the data in the same line as [5]. Fig. 5 shows schematic band diagrams (valence band edges) of devices A and B. Both

Fig. 5. Schematic band diagram (valence band edges). (a) Device A. (b) Device B. Single hole tunneling occurs through the bound states of the individual boron atoms (denoted by red bars), resulting in anomalous current peaks.

Fig. 6. (a) Activation plots of the conductance at various  $V_{GS}$  values. (b) Activation energy  $E_b$  versus  $V_{GS}$ . The extrapolation gives the threshold voltage of  $-0.65 \text{ V}$ . It suggests that the tunneling through the bound states occurs right after turn-ON.

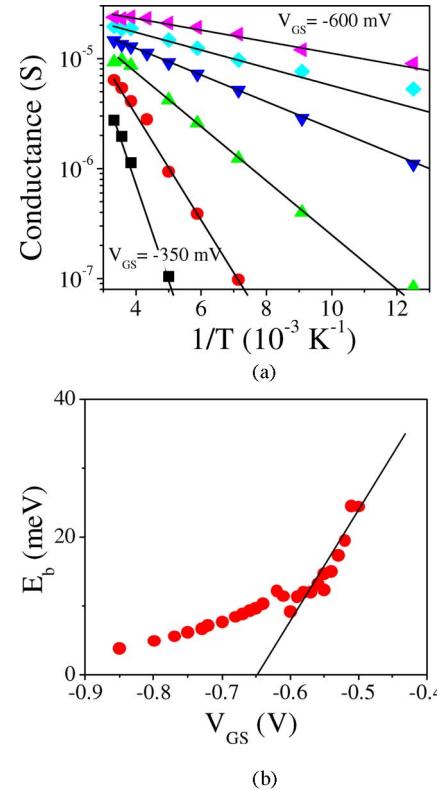

band diagrams show nanowire quantum dot with two tunnel barriers, which are formed from the gate-induced band bending of the lightly doped nanowire and the heavily doped source/drain junctions. The band diagram of device A shows two discrete impurities. The ground and the excited states of each impurity are denoted as thick lines. The four peaks denoted as I1, I2, J1, and J2 in Fig. 3(a) are tunneling through these bound states of two discrete impurities in the channel. Fig. 6(a) shows the activation plot of the low  $V_{DS}$  conductance obtained from the  $T$ -dependence in the range  $-350 \text{ mV} < V_{GS} < -600 \text{ mV}$ . Fig. 6(b) plots the obtained activation energy  $E_b$  as a function of  $V_{GS}$ . The extrapolation gives the threshold voltage of

–0.65 V. All the peaks in Fig. 3(a) are near this threshold voltage. The current peak near the threshold voltage occurs only when the Fermi level ( $E_F$ ) of the source region is aligned with the bound states of the single acceptor. The discrete acceptors probably exist near the source barrier so that the tunneling into the acceptor can result in large current peaks.

The coupling capacitances were obtained from the analysis of the Coulomb diamonds in Fig. 4 (in the entire range of  $V_{GS}$  for device B and  $V_{GS} < -0.8$  V for device A). The slopes used for the estimation of the capacitances are drawn in the figure. Device A had the gate capacitance  $C_G = 1.24$  aF, the source capacitance  $C_S = 0.65$  aF, and the drain capacitance  $C_D = 6.39$  aF, and  $\alpha = 0.15$ . Device B had  $C_G = 1.95$  aF,  $C_S = 0.63$  aF, and  $C_D = 8.7$  aF, and  $\alpha = 0.17$ . The parameters of one device are in agreement with those of another device within 20%, suggesting that the observed single hole tunneling was originated from the same quantum dots defined by the source and drain doping [12].

Using these parameters, the gate conversion factor  $\alpha = qC_G/(C_G + C_S + C_D) \approx 0.17$  (eV/V) can be obtained where  $q$  is the hole charge. This  $\alpha$  value is also consistent with  $dE_b/dV_{GS} \approx 0.16$  eV/V obtained from the solid line of Fig. 6(b). The separation between the peak positions, I1 and I2 (J1 and J2) in  $V_{GS}$ , is then converted to 25.4 meV (26.4 meV). The typical energy spacing between the bound states of boron is approximately 5 meV [14]. The Coulomb charging energy of the single acceptor is the observed energy spacing minus this bound-state energy spacing of 5 meV (resulting in 20 meV). The amount of 20 meV corresponds to the spherical dot with the radius of 3 nm if we assume the capacitance of a sphere ( $4\pi\epsilon r$ , where  $\epsilon$  is the dielectric constant of silicon and  $r$  is the radius of the dot). The obtained radius is in agreement with the Bohr radius of a light hole  $[(\epsilon\hbar^2)/(m^*q^2) = 3.9$  nm] whose effective mass  $m^*$  is 0.16 times the free electron mass.

#### IV. CONCLUSION

We performed temperature-dependent transport measurements of cylindrical-shaped GAA SNW PMOSFETs. Single hole tunneling behaviors were observed at 4.2 K, and one of the devices exhibited anomalously strong current peaks, which survived even at room temperature. The separation between two peaks with identical shapes corresponded to the energy of 25–26 meV. This value was consistent with the sum of the bound-state energy spacing of boron atom and the single-hole charging energy of a dot with 3 nm radius. This radius is also comparable to the Bohr radius of a single-acceptor atom when the light hole effective mass is used.

#### REFERENCES

- [1] H.-S. Wong and Y. Taur, “Three dimensional ‘atomistic’ simulation of discrete random dopants distribution effects in sub-0.1  $\mu$ m MOSFETs,” in *IEDM Tech. Dig.*, 1993, pp. 705–708.

- [2] L. E. Calvet, R. G. Wheeler, and M. A. Reed, “Effect of local strain on single acceptors in Si,” *Phys. Rev. B*, vol. 76, pp. 035319-1–035319-6, 2007.

- [3] M. A. H. Khalafalla, Y. Ono, K. Nishiguchi, and A. Fujiwara, “Identification of single and coupled acceptor in silicon nano-field effect transistor,” *Appl. Phys. Lett.*, vol. 91, pp. 263513-1–263513-3, 2007.

- [4] C. Ryou, S. W. Hwang, H. Shin, C. H. Lee, Y. J. Park, and H. S. Min, “Three-dimensional simulation of discrete oxide charge effects in 0.1  $\mu$ m MOSFETs,” *Solid-State Electron.*, vol. 45, pp. 1165–1172, 2001.

- [5] H. Sellier, G. P. Lansbergen, J. Caro, S. Rogge, N. Collaert, I. Ferain, M. Jurczak, and S. Biesemans, “Transport spectroscopy of a single dopant in a gated silicon nanowire,” *Phys. Rev. Lett.*, vol. 97, pp. 206805-1–206805-4, 2006.

- [6] G. P. Lansbergen, R. Rahman, C. J. Wellard, I. Woo, J. Caro, N. Collaert, S. Biesemans, G. Klimeck, L. C. Hollenberg, and S. Rogge, “Gate-induced quantum-confinement transition of a single dopant atom in a silicon FinFET,” *Nature Phys.*, vol. 4, pp. 656–661, 2008.

- [7] Y. Ono, K. Nishiguchi, A. Fujiwara, H. Yamaguchi, H. Inokawa, and Y. Takahashi, “Conductance modulation by individual acceptors in Si nanoscale field-effect transistors,” *Appl. Phys. Lett.*, vol. 90, pp. 102106-1–102106-3, Aug. 2007.

- [8] L. E. Calvet, R. G. Wheeler, and M. A. Reed, “Observation of the linear stark effect in a single acceptor in Si,” *Phys. Rev. Lett.*, vol. 98, pp. 096805-1–096805-4, 2007.

- [9] F.-L. Yang, D.-H. Lee, H.-Y. Chen, C.-Y. Chang, S.-D. Liu, C.-C. Huang, T.-X. Chung, H.-W. Chen, C.-C. Huang, Y.-H. Liu, C.-C. Wu, C.-C. Chen, S.-C. Chen, Y.-T. Chen, Y.-H. Chen, C.-J. Chen, B.-W. Chan, P.-F. Hsu, J.-H. Shieh, H.-J. Tao, Y.-C. Yeo, Y. Li, J.-W. Lee, P. Chen, M.-S. Liang, and C. Hu, “5 nm-gate nanowire FinFET,” in *Proc. Symp. VLSI Tech.*, 2004, pp. 196–197.

- [10] S. D. Suk, S.-Y. Lee, S.-M. Kim, E.-J. Yoon, M.-S. Kim, M. Li, C. W. Oh, K. H. Yeo, S. H. Kim, D.-S. Shin, K.-H. Lee, H. S. Park, J. N. Han, C. J. Park, J.-B. Park, D.-W. Kim, D. Park, and B.-I. Ryu, “High performance 5 nm radius twin silicon nanowire MOSFET (TSNWFET): Fabrication on bulk Si wafer, characteristics, and reliability,” in *IEDM Tech. Dig.*, 2005, pp. 717–720.

- [11] K. H. Cho, S. D. Suk, Y. Y. Yeo, M. Li, K. H. Yeo, D.-W. Kim, S. W. Hwang, D. Park, and B.-I. Ryu, “MOSFETs fabricated by top-down CMOS process,” in *IEDM Tech. Dig.*, 2006, pp. 543–546.

- [12] K. H. Cho, Y. C. Jung, B. H. Hong, S. W. Hwang, J. H. Oh, D. Ahn, S. D. Suk, K. H. Yeo, D.-W. Kim, D. Park, and W.-S. Lee, “Observation of three-dimensional shell filling in cylindrical silicon nanowire single electron transistors,” *Appl. Phys. Lett.*, vol. 90, pp. 182102-1–182102-3, 2007.

- [13] K. H. Cho, S. D. Suk, Y. Y. Yeo, M. Li, K. H. Yeo, D.-W. Kim, D. Park, W.-S. Lee, Y. C. Jung, B. H. Hong, and S. W. Hwang, “Temperature-dependent characteristics of cylindrical gate-all-around (GAA) twin silicon nanowire MOSFETs (TSNWFETs),” *IEEE Electron Device Lett.*, vol. 28, no. 12, pp. 1129–1131, Dec. 2007.

- [14] H. R. Chandrasekhar, A. K. Ramdas, and S. Rodriguez, “Resonant interaction of acceptor states with optical phonons in silicon,” *Phys. Rev. B*, vol. 14, pp. 2417–2421, 1976.

- [15] M. H. Huang, S. Mao, H. Feick, H. Yan, Y. Wu, H. Kind, E. Weber, R. Russo, and P. Yang, “Room-temperature ultraviolet nanowire nanolasers,” *Science*, vol. 292, no. 5523, pp. 1897–1899, 2001.

**Byoung Hak Hong** received the B.S. and M.S. degrees in electronics and computer engineering from Korea University, Seoul, Korea, in 2006 and 2008, respectively. He is currently working toward the Ph.D. degree in nanoelectronics in the Nano Electronics Lab. at Korea University.

His main research interests include characterization of silicon nanowire transistor transport mechanisms.

**Young Chai Jung** received the B.S. and M.S. degrees in electronics and computer engineering from Korea University, Seoul, Korea, in 2004 and 2006, respectively. He is currently working toward the Ph.D. degree in electronics and computer engineering in the Nano Electronics Lab. at Korea University.

His main research interests are SOI-based MOS-FETs, SOI-based single electron transistors, and silicon nanowire field effect transistors fabricated by top-down and bottom-up process.

**Jae Sung Rieh** received the B.S. and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1991 and 1995, respectively, and the Ph.D. degree in electrical engineering from the University of Michigan, Ann Arbor, in 1999.

In 1999, he joined the IBM Semiconductor R&D Center, where he was responsible for the research and development activities for the 200 GHz and 350 GHz SiGe HBT technologies. Since 2004, he has been with the School of Electrical Engineering, Korea University, Seoul, where he is currently an Associate Professor. His major interest lies in the Si-based RF devices and their application to mm-wave and terahertz circuits.

Dr. Rieh is a recipient of 2004 IBM Faculty Award and a co-recipient of 2002 and 2006 IEEE EDS George E. Smith Award. He served as the Conference Chair for 2007 Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, and is currently serving as an Associate Editor of the IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.

**Sung Woo Hwang** (M'97) received the B.S. and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1985 and 1987, respectively, and the Ph.D. degree in electrical engineering from Princeton University, Princeton, NJ, in 1993.

From 1993 to 1995, he was with the NEC Fundamental Research Laboratory, Tsukuba, Japan. Since 1995, he has been with the Department of Electronics Engineering, Korea University, Seoul, as a Professor. From 1998 to 2007, he was an Associate Director of the Institute of Quantum Information Processing and Systems, University of Seoul, Seoul. Since 2007, he is a Director of the Research Center for Time-domain Nano-functional devices, Korea University. His research interests are nanostructure fabrication, nanowire-based devices, microwave properties of quantum devices and single electron transistors, and RF/microwave passive circuit design. He has authored and coauthored more than 100 refereed international journal papers.

Dr. Hwang is a member of the American Physical Society.

**Keun Hwi Cho** (S'06–M'07) received the B.S. degree in physics and the M.S. and Ph.D. degrees in electronics and computer engineering from Korea University, Seoul, Korea, in 2001, 2003, and 2007, respectively.

In 2006, he was with the memory division in Samsung Electronics Co., Gyeonggi-Do, Korea, where he was involved in research and development of nano-CMOS transistors such as gate-all-around MOSFET and FinFET.