# 12-Bit High-Speed, Multiple SARs A/D Converter (ADC)

## HIGHLIGHTS

This section of the manual contains the following major topics:

| 1.0  | Introduction                        | 2  |

|------|-------------------------------------|----|

| 2.0  | Registers                           | 5  |

| 3.0  | Conversion Sequence                 | 36 |

| 4.0  | ADC Operation                       | 36 |

| 5.0  | Application Examples                | 57 |

| 6.0  | Operation During Power-Saving Modes | 70 |

| 7.0  | Effects of Reset                    | 70 |

| 8.0  | Register Map                        | 71 |

| 9.0  | Related Application Notes           | 75 |

| 10.0 | Revision History                    | 76 |

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC33/PIC24 devices. Please consult the note at the beginning of the chapter in the specific device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com.

## 1.0 INTRODUCTION

The dsPIC33/PIC24 12-Bit High-Speed, Multiple SARs Analog-to-Digital Converter (ADC) includes the following features:

- Multiple ADC Cores:

- Multiple single channel dedicated ADC cores (depending on the specific device implementation)

- One shared (common) ADC core

- Configurable 6, 8, 10 or 12-Bit Resolution for each ADC Core

- Up to 3.25 Msps Conversion Rate per Channel for 12-Bit Resolution

- Up to 32 Analog Input Sources (depending on the specific device implementation)

- Single-Ended or Pseudodifferential Inputs on a per Channel Basis for All Channels

- Conversion Result can be Formatted as Unsigned or Signed Data on a per Channel Basis for All Channels

- · Separate 16-Bit Conversion Result Register for each Analog Input

- Early Interrupt Generation to enable Fast Processing of Converted Data

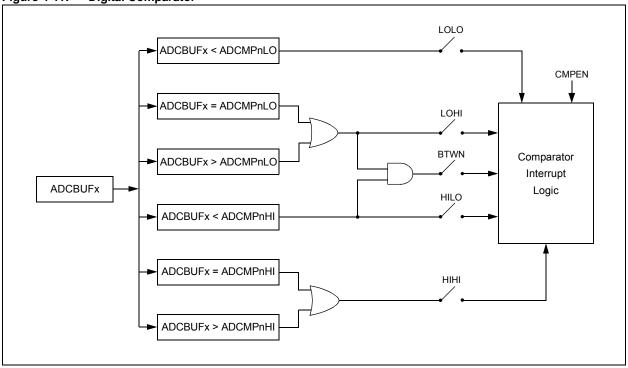

- Multiple Integrated Digital Comparators (depending on the specific device implementation):

- Multiple comparison options

- Assignable to specific analog inputs

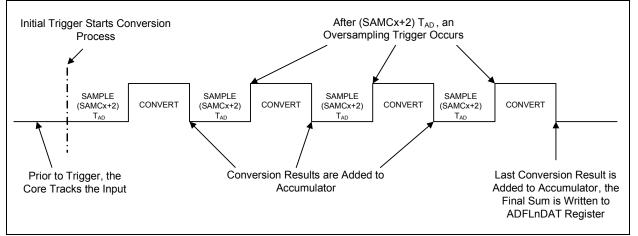

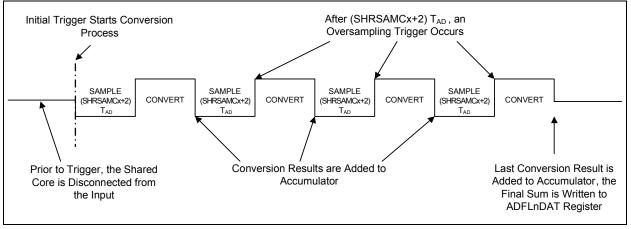

- · Multiple Oversampling Filters (depending on the specific device implementation):

- Provides increased resolution

- Assignable to a specific analog input

- · Operation during CPU Sleep and Idle modes

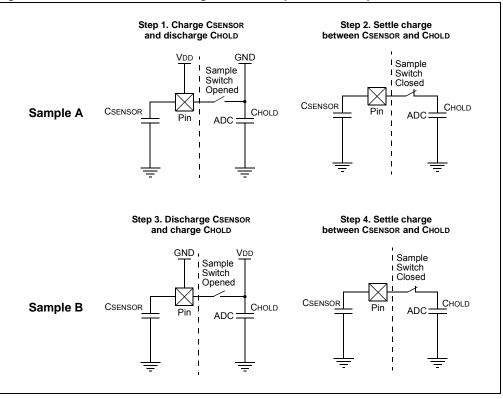

- Hardware Capacitive Voltage Divider (CVD) to Measure Capacitance Connected to the Input

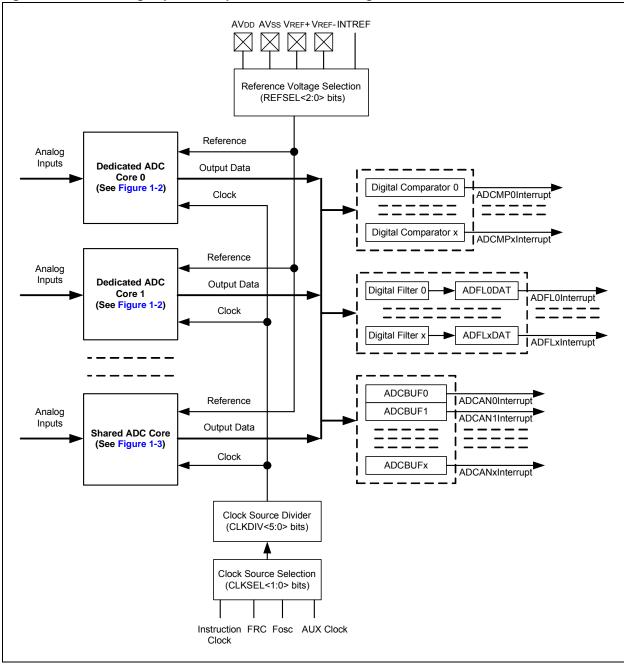

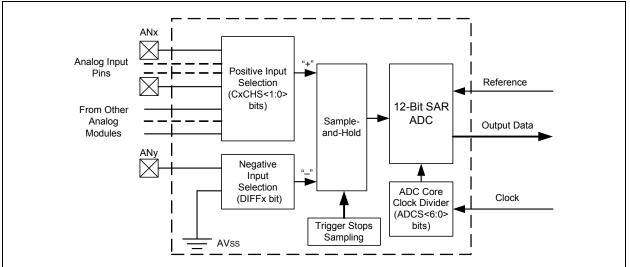

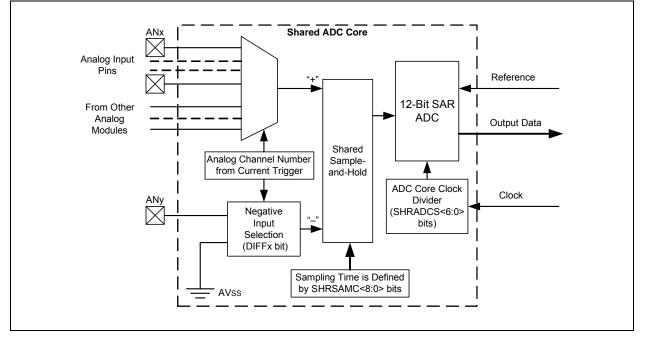

Simplified block diagrams of the Multiple SARs 12-Bit ADC are illustrated in Figure 1-1, Figure 1-2 and Figure 1-3.

The module consists of a few independent SAR ADC cores. The analog inputs (channels) are connected through multiplexers and switches to the Sample-and-Hold (S/H) circuit of each ADC core. The core uses the channel information (output format, Measurement mode and input number) to process the analog sample. When conversion is complete, the result is stored in the result buffer for the specific analog input, and passed to the digital filter and digital comparator if they were configured to use data from this particular channel.

Figure 1-1: 12-Bit High-Speed, Multiple SARs ADC Block Diagram

#### Figure 1-2: Dedicated ADC Core

## 2.0 **REGISTERS**

The Special Function Registers (SFRs) of the 12-Bit High-Speed, Multiple SARs ADC module are divided into two groups: control registers and data registers. A complete list of all SFRs implemented by the ADC is provided in Table 8-1.

#### 2.1 Control Registers

The ADCON1L register (Register 2-1) contains bits to enable the module, define the module behavior in Idle mode and enable the CVD feature.

The ADCON1H register (Register 2-2) controls the output data format and the shared ADC core resolution.

The ADCON2L register (Register 2-3) controls the clock divider and early interrupt timing selection for the shared ADC core. It has bits to enable the common interrupt for the events related to the voltage reference and a bit to enable an early interrupt feature for the individual input channels.

The ADCON2H register (Register 2-4) controls the sampling time for the shared ADC core. It also provides the status bits, which indicate that the module voltage reference is ready for operation. This register allows adjusting the internal capacitance value for the CVD feature.

The ADCON3L register (Register 2-5) selects the voltage reference for all ADC cores and controls common, level and single-shot software triggers. Also, it has control bits to suspend all triggers for the module.

The ADCON3H register (Register 2-6) has bits to enable all ADC cores and select a clock source for the module. Also, this register controls the module clock source divider.

The ADCON4L register (Register 2-7) allows enabling a delay between trigger and conversion for the dedicated ADC cores, and triggers synchronization.

The ADCON4H register (Register 2-8) selects channels for the dedicated ADC cores.

The ADCON5L register (Register 2-9) controls power for all ADC cores.

The ADCON5H register (Register 2-10) has bits to enable a common interrupt for each ADC core when it is powered on and ready for operation. Also in this register, the power-on delay is specified for all ADC cores.

The ADCOREnL (where 'n' is a dedicated ADC core number) registers (Register 2-11) define a delay between trigger and conversion for each dedicated ADC core.

The ADCOREnH (where 'n' is a dedicated ADC core number) registers (Register 2-12) define resolution, early interrupt time selection and the ADC core clock divider for each dedicated ADC core.

The ADLVLTRGL and ADLVLTRGH registers (Register 2-13 and Register 2-14) have bits to select either the level-sensitive trigger or the edge-sensitive trigger for each input channel.

The ADEIEL and ADEIEH registers (Register 2-15 and Register 2-16) have bits to enable the early interrupts generation for each input channel.

The ADEISTATL and ADEISTATH registers (Register 2-17 and Register 2-18) contain the early interrupts status flags for each input channel.

The ADMOD0L, ADMOD0H, ADMOD1L and ADMOD1H registers (Register 2-19 through Register 2-22) have bits to enable the Pseudodifferential mode and signed output data format for each input channel.

The ADIEL and ADIEH registers (Register 2-23 and Register 2-24) have bits to enable the individual and common interrupts for each input channel.

The ADSTATL and ADSTATH registers (Register 2-25 and Register 2-26) contain the data ready flags for each input channel.

The ADTRIGnL and ADTRIGnH registers (Register 2-27) define a trigger source for each input channel.

The ADCAL0L, ADCAL0H, ADCAL1L and ADCAL1H registers (Register 2-28 through Register 2-31) control the calibration for each ADC core. The calibration is not required for some devices. Refer to the specific device data sheet to see if these registers are implemented.

The ADCMPnCON registers (Register 2-32) control the operation of the digital comparators, including the generation of the interrupts and the comparison criteria to be used. These registers also provide the status when a comparator event occurs. One register is provided for each digital comparator.

The ADCMPnENL and ADCMPnENH registers (Register 2-33 and Register 2-34) select which of the analog input conversion results are to be processed by the digital comparator. One pair (L and H) is provided for each digital comparator.

The ADFLnCON registers (Register 2-35) control the operation of the oversampling filters and provide status bits for the filters' operation. One register is provided for each oversampling filter. The ADCSSL and ADCSSH registers (Register 2-36 and Register 2-37) select which of the analog inputs are to be scanned/processed by the CVD.

## 2.2 Data Registers

The ADCBUFx registers store the output data of the Analog-to-Digital conversion. In general, there is one register provided for each of the implemented analog channels; each channel will have a corresponding numbered ADCBUFx register. Although the registers are 16 bits wide, the usage of the registers for storing the 12-bit conversion results is determined by the selected data output format. See Section 4.10 "Conversion Result" for more information.

The ADCMPnLO and ADCMPnHI registers store the 16-bit high and low digital comparison values for use by the digital comparators. One pair (HI and LO) is provided for each ADC comparator.

The ADFLnDAT registers contain the 16-bit output data from the oversampling filters. There is one register for each oversampling filter.

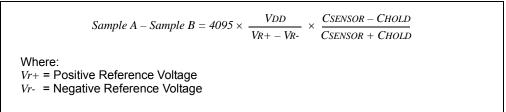

The ADCVDDAT register contains the 16-bit output data from the Capacitive Voltage Divider (CVD). This register may not be implemented on some devices. Refer to the specific device data sheet to see if the CVD feature is implemented on the device.

| Register 2-1: ADCON1L: ADC Control Register 1 Low |                              |                                                                          |               |                      |                 |                 |                 |  |  |  |  |

|---------------------------------------------------|------------------------------|--------------------------------------------------------------------------|---------------|----------------------|-----------------|-----------------|-----------------|--|--|--|--|

| R/W-0                                             | U-0                          | R/W-0                                                                    | U-0           | R/W-0                | U-0             | U-0             | U-0             |  |  |  |  |

| ADON <sup>(1)</sup>                               | —                            | ADSIDL                                                                   |               | CVDEN <sup>(2)</sup> | —               | —               | —               |  |  |  |  |

| bit 15                                            |                              | ·                                                                        |               |                      |                 |                 | bit 8           |  |  |  |  |

|                                                   |                              |                                                                          |               |                      |                 |                 |                 |  |  |  |  |

| R/W-0                                             | U-0                          | U-0                                                                      | U-0           | U-0                  | U-0             | U-0             | U-0             |  |  |  |  |

| NRE <sup>(3)</sup>                                | —                            | —                                                                        |               | —                    | —               | —               | —               |  |  |  |  |

| bit 7                                             |                              |                                                                          |               |                      |                 |                 | bit 0           |  |  |  |  |

| Legend:                                           |                              |                                                                          |               |                      |                 |                 |                 |  |  |  |  |

| R = Readal                                        | ble bit                      | W = Writable b                                                           | oit           | U = Unimplem         | ented bit, read | l as '0'        |                 |  |  |  |  |

| -n = Value a                                      | at POR                       | '1' = Bit is set                                                         |               | '0' = Bit is clea    | ared            | x = Bit is unkn | own             |  |  |  |  |

| bit 15                                            | 1 = ADC mo<br>0 = ADC mo     |                                                                          |               |                      |                 |                 |                 |  |  |  |  |

| bit 14                                            | Unimpleme                    | nted: Read as '0                                                         | ,             |                      |                 |                 |                 |  |  |  |  |

| bit 13                                            | 1 = Discontir                | OC Stop in Idle Menues module ope<br>nues module ope<br>as module operat | ration when c |                      | e mode          |                 |                 |  |  |  |  |

| bit 12                                            | Unimpleme                    | nted: Read as '0                                                         | ,             |                      |                 |                 |                 |  |  |  |  |

| bit 11                                            | CVDEN: CV                    | D Enable bit <sup>(2)</sup>                                              |               |                      |                 |                 |                 |  |  |  |  |

|                                                   | 1 = CVD is e<br>0 = CCD is c |                                                                          |               |                      |                 |                 |                 |  |  |  |  |

| bit 10-8                                          | Unimpleme                    | nted: Read as '0                                                         | ,             |                      |                 |                 |                 |  |  |  |  |

| bit 7                                             | 1 = Holds co<br>betweer      | Reduction Enabl<br>onversion proces<br>n cores<br>eduction feature       | s for 1 Tadco | RE when anothe       | r core complet  | es conversion t | o reduce noise  |  |  |  |  |

| bit 6-0                                           | Unimpleme                    | nted: Read as '0                                                         | ,             |                      |                 |                 |                 |  |  |  |  |

|                                                   |                              | bit only after the A<br>result in unpredic                               |               |                      | red. Changing   | ADC Configura   | ation bits when |  |  |  |  |

|                                                   |                              | e is not available<br>t for more infor                                   |               | s and the CVDE       | EN bit may not  | be implemented  | d. Refer to the |  |  |  |  |

|                                                   |                              | uction feature is r<br>vice data sheet fo                                |               |                      | nd the NRE bit  | may not be imp  | plemented.      |  |  |  |  |

## Register 2-1: ADCON1L: ADC Control Register 1 Low

| r-0                               | r-0                          | r-0                         | r-0                    | r-0              | r-0              | r-0                | r-0   |  |

|-----------------------------------|------------------------------|-----------------------------|------------------------|------------------|------------------|--------------------|-------|--|

| —                                 | —                            | —                           | -                      | -                | -                | —                  | —     |  |

| bit 15                            |                              |                             |                        |                  |                  |                    | bit 8 |  |

| [                                 |                              |                             |                        |                  |                  |                    |       |  |

| R/W-0                             | R/W-1                        | R/W-1                       | r-0                    | r-0              | r-0              | r-0                | r-0   |  |

| FORM                              | SHRRES1                      | SHRRES0                     |                        |                  |                  |                    |       |  |

| bit 7                             |                              |                             |                        |                  |                  |                    | bit 0 |  |

| Lonordi                           |                              | n – Decemied                | L:4                    |                  |                  |                    |       |  |

| Legend:                           |                              | r = Reserved                |                        |                  |                  |                    |       |  |

| R = Readable bit W = Writable bit |                              |                             |                        | -                | nented bit, read |                    |       |  |

| -n = Value a                      | t POR                        | '1' = Bit is set            | t '0' = Bit is cleared |                  | ared             | x = Bit is unknown |       |  |

|                                   | Deserved M                   |                             | (0)                    |                  |                  |                    |       |  |

| bit 15-8                          |                              | ust be written a            |                        |                  |                  |                    |       |  |

| bit 7                             |                              | ional Data Out <sub>l</sub> | put Format bit         |                  |                  |                    |       |  |

|                                   | 1 = Fractiona<br>0 = Integer | I                           |                        |                  |                  |                    |       |  |

| bit 6-5                           | SHRRES<1:0                   | <b>)&gt;:</b> Shared AD     | C Core Resolut         | tion Selection b | its              |                    |       |  |

|                                   | 11 = 12-bit re               | solution                    |                        |                  |                  |                    |       |  |

|                                   | 10 = 10-bit re               | solution                    |                        |                  |                  |                    |       |  |

|                                   | 01 = 8-bit resolution        |                             |                        |                  |                  |                    |       |  |

|                                   | 00 <b>= 6-bit res</b>        | olution                     |                        |                  |                  |                    |       |  |

| bit 4-0                           | Reserved: M                  | ust be written a            | <b>as</b> '0'          |                  |                  |                    |       |  |

|                                   |                              |                             |                        |                  |                  |                    |       |  |

|                                   |                              |                             |                        |                  |                  |                    |       |  |

## Register 2-2: ADCON1H: ADC Control Register 1 High

r-0

R/W-0

R/W-0

R/W-0

R/W-0

| REFCIE     | REFERCIE <sup>(2)</sup>         | —                | EIEN           | —                 | SHREISEL2(1)                      | SHREISEL1(1)              | SHREISEL0 <sup>(1)</sup> |

|------------|---------------------------------|------------------|----------------|-------------------|-----------------------------------|---------------------------|--------------------------|

| bit 15     |                                 |                  |                |                   |                                   |                           | bit 8                    |

|            |                                 |                  |                |                   |                                   |                           |                          |

| U-0        | R/W-0                           | R/W-0            | R/W-0          | R/W-0             | R/W-0                             | R/W-0                     | R/W-0                    |

| _          | SHRADCS6                        | SHRADCS5         | SHRADCS4       | SHRADCS3          | SHRADCS2                          | SHRADCS1                  | SHRADCS0                 |

| bit 7      |                                 | I                |                |                   | 1                                 | 1                         | bit 0                    |

|            |                                 |                  |                |                   |                                   |                           |                          |

| Legend:    |                                 | r = Reserved     | bit            |                   |                                   |                           |                          |

| R = Reada  | able bit                        | W = Writable     | bit            | U = Unimplen      | nented bit, read                  | as '0'                    |                          |

| -n = Value | at POR                          | '1' = Bit is set |                | '0' = Bit is clea |                                   | x = Bit is unkno          | wn                       |

|            |                                 |                  |                |                   |                                   |                           |                          |

| bit 15     | REECIE: Ban                     | d Gap and Re     | ference Voltag | es Ready Com      | mon Interrupt E                   | nable bit                 |                          |

|            |                                 | -                | -              | -                 | -                                 | oltage are ready          |                          |

|            |                                 | •                | •              | • •               | ence voltage rea                  | • •                       |                          |

| bit 14     | REFERCIE: E                     | Band Gap and     | Reference Vol  | tages Error Co    | mmon Interrupt                    | Enable bit <sup>(2)</sup> |                          |

|            |                                 |                  |                |                   |                                   | age error is dete         | ected                    |

|            | 0 = Common                      | interrupt is dis | abled for band | gap and refere    | ence voltages er                  | ror event                 |                          |

| bit 13     | Reserved: M                     | ust be written   | <b>as</b> '0'  |                   |                                   |                           |                          |

| bit 12     | -                               | nterrupts Enab   |                |                   |                                   |                           |                          |

|            |                                 |                  |                |                   |                                   | (when the EIST/           |                          |

| 1.11.4.4   |                                 | -                | •              | when the conv     | Persion is done                   | when the ANxR             | (DY flag is set)         |

| bit 11     |                                 | ust be written   |                |                   |                                   |                           |                          |

| bit 10-8   |                                 |                  |                | rupt Time Sele    |                                   |                           |                          |

|            |                                 |                  |                |                   | to when the date to when the date |                           |                          |

|            |                                 |                  |                |                   | to when the da                    |                           |                          |

|            |                                 |                  |                |                   | to when the da                    |                           |                          |

|            |                                 |                  |                |                   | to when the da                    |                           |                          |

|            |                                 |                  |                |                   | to when the da                    |                           |                          |

|            |                                 |                  |                |                   | to when the date                  |                           |                          |

| bit 7      | -                               | ted: Read as '   |                |                   |                                   | lisiteday                 |                          |

| bit 6-0    | -                               |                  |                | Clock Divider     | hits                              |                           |                          |

| bit 0 0    |                                 |                  | -              |                   |                                   | for one shared            | TADCORE (Core            |

|            | Clock Period)                   |                  |                |                   |                                   |                           |                          |

|            |                                 | 54 source cloc   | k periods      |                   |                                   |                           |                          |

|            | •                               |                  |                |                   |                                   |                           |                          |

|            | •                               |                  |                |                   |                                   |                           |                          |

|            | 0000011 = 6                     | source clock p   | periods        |                   |                                   |                           |                          |

|            |                                 | source clock p   |                |                   |                                   |                           |                          |

|            |                                 | source clock p   |                |                   |                                   |                           |                          |

|            | 0000000 = 2                     | source clock p   | periods        |                   |                                   |                           |                          |

| Note 1:    | For the 6-bit sha               | ared ADC core    | resolution (SF | IRRES<1:0> =      | 00), the SHREI                    | SEL<2:0> settir           | igs, from                |

|            | '100' <b>to</b> '111', <b>a</b> |                  |                |                   |                                   |                           |                          |

|            | (SHRRES<1:0>                    | • = 01), the SH  | REISEL<2:0>    | settings, '110' a | and '111', are no                 | ot valid and sho          | uld not be used.         |

|            |                                 |                  |                |                   |                                   |                           |                          |

## Register 2-3: ADCON2L: ADC Control Register 2 Low

r-0

R/W-0

R/W-0

2: To avoid false interrupts, the REFERCIE bit must be set only after the module is enabled (ADON = 1).

| R/HS/HC-0       | R/HS/HC-0                                                                                                                                                    | r-0                                                                                                                    | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0           | R/W-0         |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|-----------------|---------------|--|--|--|--|

| REFRDY          | REFERR                                                                                                                                                       | —                                                                                                                      | CVDCAP2 <sup>(1)</sup> | CVDCAP1 <sup>(1)</sup> | CVDCAP0 <sup>(1)</sup> | SHRSAMC9        | SHRSAMC8      |  |  |  |  |

| bit 15          |                                                                                                                                                              |                                                                                                                        |                        | •                      |                        |                 | bit 8         |  |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                        |                        |                        |                        |                 |               |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                        | R/W-0                                                                                                                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0           | R/W-0         |  |  |  |  |

| SHRSAMC7        | SHRSAMC6                                                                                                                                                     | SHRSAMC5                                                                                                               | SHRSAMC4               | SHRSAMC3               | SHRSAMC2               | SHRSAMC1        | SHRSAMC0      |  |  |  |  |

| bit 7           |                                                                                                                                                              |                                                                                                                        |                        |                        |                        |                 | bit 0         |  |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                        |                        |                        |                        |                 |               |  |  |  |  |

| Legend:         |                                                                                                                                                              | HC = Hardware                                                                                                          | Clearable bit          | HS = Hardware          | e Settable bit         | r = Reserved    | bit           |  |  |  |  |

| R = Readable    | = Readable bit W = Writable bit                                                                                                                              |                                                                                                                        |                        | U = Unimplem           | ented bit, read        | as '0'          |               |  |  |  |  |

| -n = Value at l | POR                                                                                                                                                          | '1' = Bit is set                                                                                                       |                        | '0' = Bit is clea      | ared                   | x = Bit is unkn | iown          |  |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                        |                        |                        |                        |                 |               |  |  |  |  |

| bit 15          | REFRDY: Bar                                                                                                                                                  | nd Gap and Refe                                                                                                        | erence Voltages        | s Ready Flag bi        | t                      |                 |               |  |  |  |  |

|                 | 1 = Band gap and reference voltages are ready                                                                                                                |                                                                                                                        |                        |                        |                        |                 |               |  |  |  |  |

|                 | ÷ .                                                                                                                                                          | and reference v                                                                                                        | -                      | -                      |                        |                 |               |  |  |  |  |

| bit 14          | <b>REFERR:</b> Band Gap or Reference Voltage Error Flag bit<br>1 = Band gap or reference voltage was interrupted after the ADC module was enabled (ADON = 1) |                                                                                                                        |                        |                        |                        |                 |               |  |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                        |                        |                        | ADC module w           | as enabled (A   | DON = 1)      |  |  |  |  |

| bit 13          | <ul> <li>0 = No band gap or reference voltage error was detected</li> <li>Reserved: Must be written as '0'</li> </ul>                                        |                                                                                                                        |                        |                        |                        |                 |               |  |  |  |  |

| bit 12-10       |                                                                                                                                                              | <ul> <li>CVD Addition</li> </ul>                                                                                       |                        | Selection hits         | 1)                     |                 |               |  |  |  |  |

|                 |                                                                                                                                                              | nce is added to<br>pF = 17.5 pF<br>pF = 15 pF<br>pF = 12.5 pF<br>pF = 10 pF<br>pF = 7.5 pF<br>pF = 5 pF<br>pF = 2.5 pF |                        |                        |                        | ance (CHOLD)    | when CVD is   |  |  |  |  |

| bit 9-0         | SHRSAMC<2                                                                                                                                                    | :0>: Shared AD                                                                                                         | C Core Sample          | e Time Selection       | n bits                 |                 |               |  |  |  |  |

|                 | sample time.                                                                                                                                                 |                                                                                                                        |                        | Core Clock Per         | iods (Tadcore          | E) for the shar | red ADC core  |  |  |  |  |

| Note 1: Th      | e CVD feature                                                                                                                                                | is not available                                                                                                       | on all devices a       | nd the CVDCA           | ><2:0> bits ma         | v not be impler | nented. Refer |  |  |  |  |

### Register 2-4: ADCON2H: ADC Control Register 2 High

**Note 1:** The CVD feature is not available on all devices and the CVDCAP<2:0> bits may not be implemented. Refer to the device data sheet for more information.

|                        |                                                                                                                                                                                                                                                                   |                                                                                                                          | •                                                                                            |                                                                     |                                              |                               |                |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------|-------------------------------|----------------|--|--|--|

| R/W-0                  | R/W-0                                                                                                                                                                                                                                                             | R/W-0                                                                                                                    | R/W-0                                                                                        | R/W-0                                                               | R/HS/HC-0                                    | R/W-0                         | R/W/HC-0       |  |  |  |

| REFSEL2 <sup>(1)</sup> | REFSEL1 <sup>(1)</sup>                                                                                                                                                                                                                                            | REFSEL0 <sup>(1)</sup>                                                                                                   | SUSPEND                                                                                      | SUSPCIE                                                             | SUSPRDY                                      | SHRSAMP                       | CNVRTCH        |  |  |  |

| bit 15                 |                                                                                                                                                                                                                                                                   |                                                                                                                          |                                                                                              |                                                                     |                                              |                               | bit 8          |  |  |  |

|                        |                                                                                                                                                                                                                                                                   |                                                                                                                          |                                                                                              |                                                                     |                                              |                               |                |  |  |  |

| R/W-0                  | R/W/HC-0                                                                                                                                                                                                                                                          | R/W-0                                                                                                                    | R/W-0                                                                                        | R/W-0                                                               | R/W-0                                        | R/W-0                         | R/W-0          |  |  |  |

| SWLCTRG                | SWCTRG                                                                                                                                                                                                                                                            | CNVCHSEL5                                                                                                                | CNVCHSEL4                                                                                    | CNVCHSEL3                                                           | CNVCHSEL2                                    | CNVCHSEL1                     | CNVCHSEL0      |  |  |  |

| bit 7                  |                                                                                                                                                                                                                                                                   |                                                                                                                          |                                                                                              |                                                                     |                                              |                               | bit 0          |  |  |  |

|                        |                                                                                                                                                                                                                                                                   |                                                                                                                          |                                                                                              |                                                                     |                                              |                               |                |  |  |  |

| Legend:                |                                                                                                                                                                                                                                                                   | HC = Hardware                                                                                                            | Clearable bit                                                                                | HS = Hardware                                                       | e Settable bit                               |                               |                |  |  |  |

| R = Readable           | e bit                                                                                                                                                                                                                                                             | W = Writable bi                                                                                                          | t                                                                                            | U = Unimplem                                                        | ented bit, read                              | as '0'                        |                |  |  |  |

| -n = Value at          | POR                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                         |                                                                                              | '0' = Bit is clea                                                   | red                                          | x = Bit is unkr               | nown           |  |  |  |

|                        |                                                                                                                                                                                                                                                                   | >: ADC Referen<br>II ADC Cores Tr                                                                                        | -                                                                                            |                                                                     |                                              |                               |                |  |  |  |

|                        |                                                                                                                                                                                                                                                                   | gger events for                                                                                                          |                                                                                              |                                                                     |                                              |                               |                |  |  |  |

|                        |                                                                                                                                                                                                                                                                   | ores can be trigg                                                                                                        |                                                                                              |                                                                     |                                              |                               |                |  |  |  |

| bit 11                 | SUSPCIE: Su                                                                                                                                                                                                                                                       | Ispend All ADC                                                                                                           | -<br>Cores Common                                                                            | Interrupt Enab                                                      | le bit                                       |                               |                |  |  |  |

|                        | <ul> <li>1 = Common interrupt will be generated when ADC cores triggers are suspended (SUSPEND bit = 1) and all previous conversions are finished (SUSPRDY bit becomes set)</li> <li>0 = Common interrupt is not generated for suspend ADC cores event</li> </ul> |                                                                                                                          |                                                                                              |                                                                     |                                              |                               |                |  |  |  |

| h# 10                  |                                                                                                                                                                                                                                                                   |                                                                                                                          | -                                                                                            | =                                                                   | ores event                                   |                               |                |  |  |  |

| bit 10                 | 1 = All ADC c                                                                                                                                                                                                                                                     | II ADC Cores Su<br>ores are suspen<br>s have previous                                                                    | ded (SUSPEN                                                                                  | D bit = 1) and h                                                    | ave no convers                               | sions in progres              | SS             |  |  |  |

| bit 9                  |                                                                                                                                                                                                                                                                   | Shared ADC Cor                                                                                                           |                                                                                              |                                                                     |                                              |                               |                |  |  |  |

|                        | This bit should<br>connects an a<br>extending the<br>conversion sta<br>1 = Shared Al                                                                                                                                                                              | d be used with the<br>analog input spectrum<br>sampling time.<br>arts (setting CNV<br>DC core sample<br>is controlled by | ne individual ch<br>ecified by the C<br>This bit is not<br>/RTCH to '1').<br>s an analog inp | annel conversio<br>CNVCHSEL<5:0<br>controlled by<br>ut specified by | bits to the s<br>hardware and<br>the CNVCHSE | hared ADC co<br>must be clear | re and allows  |  |  |  |

| bit 8                  | CNVRTCH: S                                                                                                                                                                                                                                                        | oftware Individu                                                                                                         | al Channel Cor                                                                               | version Trigger                                                     | <sup>-</sup> bit                             |                               |                |  |  |  |

|                        | is set, it is                                                                                                                                                                                                                                                     | gger is generate<br>s automatically c<br>vidual channel c                                                                | leared by hard                                                                               | ware on the nex                                                     | t instruction cy                             |                               | ; when the bit |  |  |  |

| bit 7                  | SWLCTRG: S                                                                                                                                                                                                                                                        | Software Level-S                                                                                                         | ensitive Comm                                                                                | on Trigger bit                                                      |                                              |                               |                |  |  |  |

|                        | trigger is                                                                                                                                                                                                                                                        | are continuously<br>selected as a so<br>are level-sensitiv                                                               | ource in the AD                                                                              | TRIGnL and AD                                                       | TRIGnH regist                                |                               | itive common   |  |  |  |

| bit 6                  |                                                                                                                                                                                                                                                                   | oftware Commor                                                                                                           |                                                                                              |                                                                     |                                              |                               |                |  |  |  |

|                        | 1 = Single trig<br>in the AI<br>hardware                                                                                                                                                                                                                          | gger is generated<br>DTRIGnL and A<br>on the next inst<br>generate the ne                                                | d for all channel<br>DTRIGnH regi<br>ruction cycle                                           | sters; when the                                                     |                                              |                               |                |  |  |  |

|                        | CNVCHSEL<                                                                                                                                                                                                                                                         |                                                                                                                          |                                                                                              |                                                                     |                                              |                               |                |  |  |  |

#### Register 2-5: ADCON3L: ADC Control Register 3 Low

| R/W-0        | R/W-0                                                                                                                                                                                                | R/W-0                          | R/W-0               | R/W-0                          | R/W-0               | R/W-0               | R/W-0               |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------|--------------------------------|---------------------|---------------------|---------------------|--|--|--|--|

| CLKSEL1(     | ) CLKSEL0 <sup>(1)</sup>                                                                                                                                                                             | CLKDIV5                        | CLKDIV4             | CLKDIV3                        | CLKDIV2             | CLKDIV1             | CLKDIV0             |  |  |  |  |

| bit 15       |                                                                                                                                                                                                      |                                |                     |                                |                     |                     | bit 8               |  |  |  |  |

|              |                                                                                                                                                                                                      |                                |                     |                                |                     |                     |                     |  |  |  |  |

| R/W-0        | R/W-0                                                                                                                                                                                                | R/W-0                          | R/W-0               | R/W-0                          | R/W-0               | R/W-0               | R/W-0               |  |  |  |  |

| SHREN        | C6EN <sup>(2)</sup>                                                                                                                                                                                  | C5EN <sup>(2)</sup>            | C4EN <sup>(2)</sup> | C3EN <sup>(2)</sup>            | C2EN <sup>(2)</sup> | C1EN <sup>(2)</sup> | C0EN <sup>(2)</sup> |  |  |  |  |

| bit 7        | bi                                                                                                                                                                                                   |                                |                     |                                |                     |                     |                     |  |  |  |  |

| Legend:      |                                                                                                                                                                                                      |                                |                     |                                |                     |                     |                     |  |  |  |  |

| R = Readal   | ole bit                                                                                                                                                                                              | W = Writable                   | bit                 | U = Unimpleme                  | ented bit, read a   | as 'O'              |                     |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                                                               | '1' = Bit is set               |                     | '0' = Bit is clea              | red                 | x = Bit is unk      | nown                |  |  |  |  |

|              |                                                                                                                                                                                                      |                                |                     |                                |                     |                     |                     |  |  |  |  |

| bit 15-14    | CLKSEL<1:0                                                                                                                                                                                           | >: ADC Modul                   | e Clock Source      | e Selection bits <sup>(1</sup> | )                   |                     |                     |  |  |  |  |

| bit 13-8     | CLKDIV<5:0>                                                                                                                                                                                          | -: ADC Module                  | e Clock Source      | Divider bits                   |                     |                     |                     |  |  |  |  |

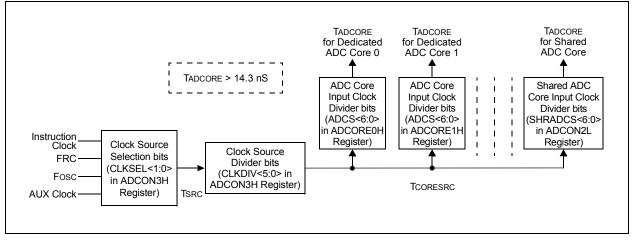

|              | The divider fo                                                                                                                                                                                       | rms a TCORES                   | RC clock used b     | ov all ADC cores               | (shared and de      | dicated) from t     | he TSRC ADC         |  |  |  |  |

|              | The divider forms a TCORESRC clock used by all ADC cores (shared and dedicated) from the TSRC ADC module clock source selected by the CLKSEL<1:0> bits. Then, each ADC core individually divides the |                                |                     |                                |                     |                     |                     |  |  |  |  |

|              | TCORESRC clock to get a core-specific TADCORE clock, using the ADCS<6:0> bits in the ADCOREnH                                                                                                        |                                |                     |                                |                     |                     |                     |  |  |  |  |

|              |                                                                                                                                                                                                      |                                |                     | ADCON2L regis                  |                     |                     |                     |  |  |  |  |

|              | 111111 = 64                                                                                                                                                                                          |                                |                     |                                |                     |                     |                     |  |  |  |  |

|              | •                                                                                                                                                                                                    |                                |                     |                                |                     |                     |                     |  |  |  |  |

|              | •                                                                                                                                                                                                    |                                |                     |                                |                     |                     |                     |  |  |  |  |

|              | •                                                                                                                                                                                                    |                                |                     |                                |                     |                     |                     |  |  |  |  |

|              | 000011 <b>= 4 s</b>                                                                                                                                                                                  | ource clock pe                 | eriods              |                                |                     |                     |                     |  |  |  |  |

|              | 000010 = 3 s                                                                                                                                                                                         | ource clock pe                 | eriods              |                                |                     |                     |                     |  |  |  |  |

|              | 000001 = 2 source clock periods                                                                                                                                                                      |                                |                     |                                |                     |                     |                     |  |  |  |  |

|              | 000000 = 1 s                                                                                                                                                                                         | 000000 = 1 source clock period |                     |                                |                     |                     |                     |  |  |  |  |

| bit 7        | SHREN: Shar                                                                                                                                                                                          | red ADC Core                   | Enable bit          |                                |                     |                     |                     |  |  |  |  |

|              | This bit does                                                                                                                                                                                        | not disable the                | e core clock and    | d analog bias cir              | cuitry.             |                     |                     |  |  |  |  |

|              | 1 = Shared Al                                                                                                                                                                                        | DC core is ena                 | abled               |                                |                     |                     |                     |  |  |  |  |

|              |                                                                                                                                                                                                      | DC core is disa                |                     |                                |                     |                     |                     |  |  |  |  |

| bit 6-0      | C6EN:C0EN:                                                                                                                                                                                           | Dedicated AD                   | C Core x Enab       | ole bits <sup>(2)</sup>        |                     |                     |                     |  |  |  |  |

|              |                                                                                                                                                                                                      |                                |                     | d analog bias cir              | cuitry.             |                     |                     |  |  |  |  |

|              | 1 = Dedicated                                                                                                                                                                                        |                                |                     |                                |                     |                     |                     |  |  |  |  |

|              | 0 = Dedicated                                                                                                                                                                                        | I ADC Core x i                 | s disabled          |                                |                     |                     |                     |  |  |  |  |

| Note 1:      | Refer to the spec                                                                                                                                                                                    | ific device dat                | a sheet for the     | available ADC n                | nodule clock so     | urce options.       |                     |  |  |  |  |

|              | The number of th                                                                                                                                                                                     |                                |                     |                                |                     |                     | av not be           |  |  |  |  |

|              | mplemented. Re                                                                                                                                                                                       |                                |                     |                                |                     |                     | .,                  |  |  |  |  |

|              |                                                                                                                                                                                                      |                                |                     |                                |                     |                     |                     |  |  |  |  |

## Register 2-6: ADCON3H: ADC Control Register 3 High

| U-0    | r-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

#### Register 2-7: ADCON4L: ADC Control Register 4 Low

| U-0   | R/W-0                  |

|-------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _     | SAMC6EN <sup>(1)</sup> | SAMC5EN <sup>(1)</sup> | SAMC4EN <sup>(1)</sup> | SAMC3EN <sup>(1)</sup> | SAMC2EN <sup>(1)</sup> | SAMC1EN <sup>(1)</sup> | SAMC0EN <sup>(1)</sup> |

| bit 7 |                        |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  | r = Reserved bit       | r = Reserved bit                   |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

bit 15 Unimplemented: Read as '0'

bit 14-8 **Reserved:** Must be written as '0'

bit 7 Unimplemented: Read as '0'

bit 6-0 SAMC6EN: SAMC0EN: Dedicated ADC Core x Conversion Delay Enable bits<sup>(1)</sup>

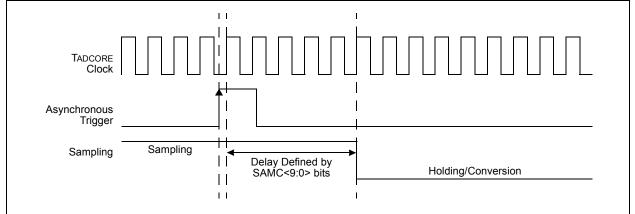

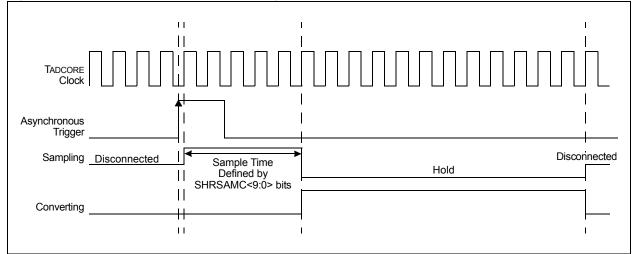

- 1 = After the trigger, the conversion will be delayed and the ADC core will continue sampling during the time specified by the SAMC<9:0> bits in the ADCOREnL register

- 0 = After the trigger, the sampling will be stopped immediately and the conversion will be started on the next core clock cycle

- **Note 1:** The number of available dedicated ADC cores is device-specific and some SAMCxEN bits may not be implemented. Refer to the device data sheet for more information.

| U-0                   | U-0                                                                                  | R/W-0                                                                                | R/W-0                 | R/W-0                              | R/W-0                     | R/W-0                 | R/W-0                 |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------|------------------------------------|---------------------------|-----------------------|-----------------------|--|--|--|--|

| _                     | —                                                                                    | C6CHS1 <sup>(1)</sup>                                                                | C6CHS0 <sup>(1)</sup> | C5CHS1 <sup>(1)</sup>              | C5CHS0 <sup>(1)</sup>     | C4CHS1 <sup>(1)</sup> | C4CHS0 <sup>(1)</sup> |  |  |  |  |

| bit 15                |                                                                                      |                                                                                      |                       |                                    |                           |                       | bit 8                 |  |  |  |  |

|                       |                                                                                      |                                                                                      |                       |                                    |                           |                       |                       |  |  |  |  |

| R/W-0                 | R/W-0                                                                                | R/W-0                                                                                | R/W-0                 | R/W-0                              | R/W-0                     | R/W-0                 | R/W-0                 |  |  |  |  |

| C3CHS1 <sup>(1)</sup> | C3CHS0 <sup>(1)</sup>                                                                | C2CHS1 <sup>(1)</sup>                                                                | C2CHS0 <sup>(1)</sup> | C1CHS1 <sup>(1)</sup>              | C1CHS0 <sup>(1)</sup>     | C0CHS1 <sup>(1)</sup> | C0CHS0 <sup>(1)</sup> |  |  |  |  |