Bonsoir,

J'ai un gros doute sur la méthode de dimensionnement de la résistance de grille d'un transistor MOSFET.

Je n'ai pas d'application précise, c'est juste pour comprendre ce qu'il faut prendre en compte.

J'ai cherché sur le forum mais bien souvent les discussions s'arrêtent sur "met tel valeur est ça ira" et disons que j'espérais avoir un poil plus d'explication.

Voilà ce que moi je comprends en voyant ceci : https://www.fairchildsemi.com/datash.../RFD3055LE.pdf avec l'hypothèse que je commande mon VGS en logique +5V

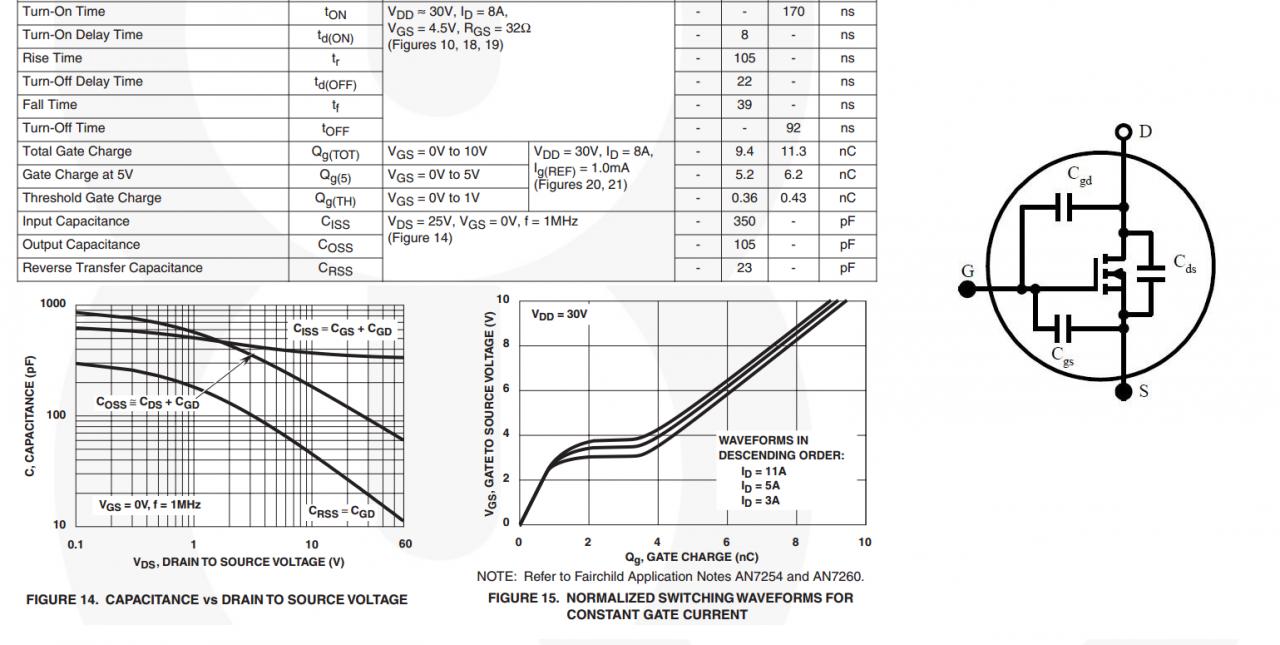

Je vois deux capacités parasites Cgs, Cgd, qui vont créer un appel de courant, en fonction du temps de monté du signal de commande, sur la grille. A prendre en compte

Je sais que si j'applique un signal périodique (PWM ou carré, ...) sur ma grille, je vais me retrouver avec une impédance de environ 1/(Ciss * 2 * PI * F) et donc m'assurer de la sortance de ma porte logique. A prendre en compte

Si VDS varie trop vite et pour ça je dois regarder tr et tf, Cgd (retour de boomerang) va créer un appel de courant sur mon signal de commande et si j'ai pas de bol (appel trop fort et ma tension de grille s'effondre), le transistor change d'état. A prendre en compte

Lors du blocage du transistor est bloqué, il faudra que j'évacue les courants en faisant attention de ne pas casser ma porte logique en dépassant son IIL. A prendre en compte

Heu... c'est bien pour la raison ci dessus que l'on met une résistance de grille ? Quelqu'un peut il confirmer ?

Je comprends aussi qu'en cas de mise hors tension de l'électronique en général, ces capacités d'entrée vont me causer un effet mémoire. Pull down sur la grille

La figure 15 montre un plateau Miller, je sais que c'est causé par Cgd mais je ne sais plus qu'est ce qui se passe. Quelqu'un peut il m'éclairer, pas forcément dans le détail mathématique ?

Etant donné ce plateau, c'est bien ça durée qui risque de ne pas faire du bien au transistor puisqu'il n'est pas saturé et il va dissiper fortement durant un temps Qg(5), pour mon exemple. J'imagine que c'est bien ça qu'il faut que je regarde ?

Je peux trouver une constante de temps en multipliant une résistance de grille avec (Qg(5) / VGS) Je me retrouve avec un temps où le transistor va dissiper mais qu'elle rapport avec la résistance de grille ?

Bon, déjà j'espère ne pas être complètement a coté de la plaque pour le moment et maintenant c'est qu'est ce que je fais de tout ça et par quel bout je le prends pour dimensionner une résistance de grille ?

D'avance merci.

Vincent

-----

je me disais aussi !!!! Quand j'ai écrit que je n'y avais pas pensé, je m'étais dit après coup.... la vache

je me disais aussi !!!! Quand j'ai écrit que je n'y avais pas pensé, je m'étais dit après coup.... la vache