Bonjour,

Je dispose d'une carte contenant 16 "pixels" avec 3 leds (rouge, vert et bleu) par pixel ainsi que d'un XC2C128 VQ100.

Le but est de créer diverses animations, changer de couleurs etc...

Je souhaiterais dans un premier temps découper mes 48 leds en pack de 3 pour former 16 pixels que je commanderais par la suite.

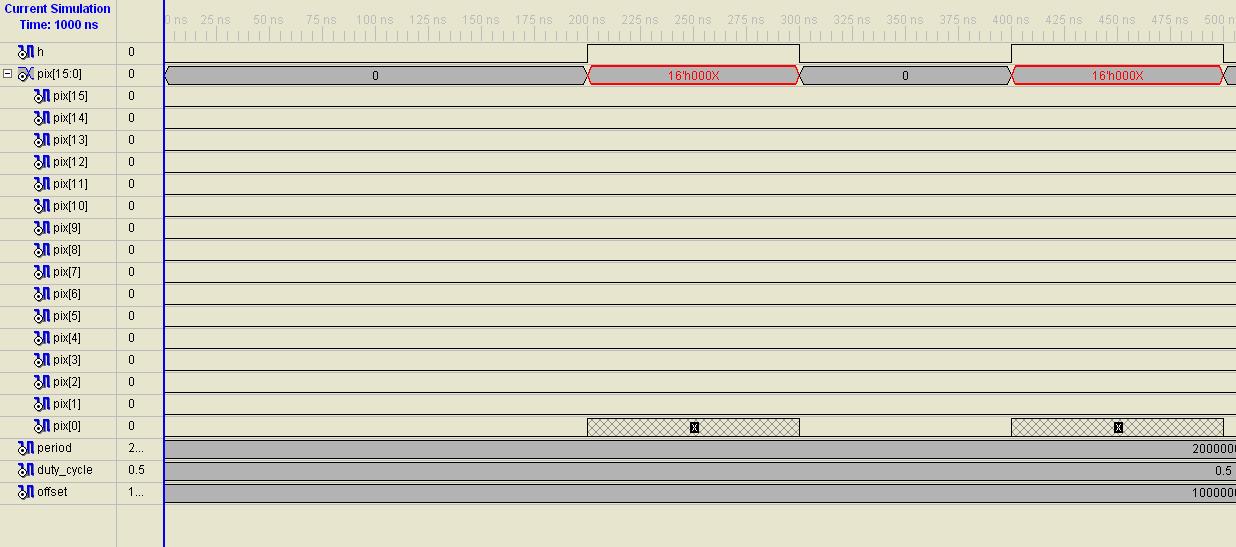

J'ai donc dans mon VHDL ma sortie STD_LOGIC_VECTOR (47 DOWNTO 0) et mon horloge en entrée.

Ce que j'aimerais faire c'est "modifier" mes sorties pour ne plus avoir 48 leds à commander mais 16 packs de leds.

Le problème c'est que je n'ai aucune idée sur quoi partir pour commencer mon code

J'ai pensez créer un signal pixel par exemple (15 downto 0) puis faire des tableaux (16).

Par exemple:

pixel(0) aura la table 1, pixel(2) aura la table 2 etc... jusqu'a 16 afin de ne plus manipuler led(0),led(1) jusqu'à 47 mais pixel(0),pixel(1) etc... jusqu'à 15Code:signal pixel : STD_LOGIC_VECTOR (15 downto 0); type table is array (0 to 15) of std_logic_vector (47 downto 0); constant pixel_table : table := ( "000 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111", "111 000 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111 111", .... x16 pour chaque pixel Begin pixel <= pixel_table;

Ce code est faux, il y aura plein d'erreur, mais c'est la seul façon que j'ai trouvé pour expliquer ce que je cherche à réaliser. De plus il y aura surment des problèmes si j'allume 2 pixels en même temps avec cette idée.

Ou sinon créer mon signal pixel, puis faire 16x:

pixel(0) <= not(led(0)) AND not(led(1)) AND not(led(2));

etc...

Pourriez-vous me donner un petit coups de pouce ?

Je vous en remercie

PS: mes leds s'allume à l'état bas, j'ai toutes les infos du mapping des leds sur les I/O du CPLD.

-----