Bonjour,

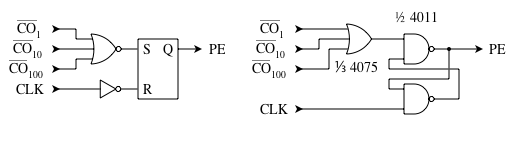

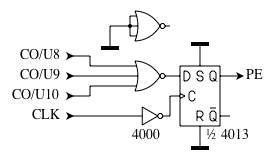

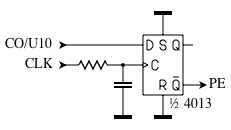

Je suis en train de mettre au point un diviseur programmable pour une PLL en synthétiseur de fréquences. J'utilise 3 circuits 4510 en décompteurs que jinitialise à une valeur comprise entre 1 et 999. Lorsque les 3 compteurs sont en fin de cycle, leur sorties /CO passent à 0, et je me sert de ça pour activer en même temps les 3 entrées de chargement parallèle à travers un NOR pour remettre l'ensemble à la valeur définie par les 12 bits en entrée. Et le cycle recommence. Ce montage est donc un diviseur programmable

Jusque là, tout va bien, mais je me pose deux questions :

1)

Le pulse en sortie du NOR est très court car sitôt l'info de chargement parallèle envoyée, les /CO se remettent à 1, et je me dis qu'un des compteurs peut fonctionner plus lentement que les autres, et ne comprenne pas à temps qu'il faut se recharger à la valeur de base. A la simulation, ça marche, mais je n'ai pas testé en vrai. Ce risque existe t-il vraiment ?

2)

Le pulse en sortie du NOR étant très court, es ce que ce signal peut être utilisé sur le comparateur 3 états du circuit PLL 4046 ?

Je sais que ce circuit détecte les fronts montants, et non les états logiques, mais vu qu'ils sont très brefs, je me demande si ça ne va pas poser problème

Merci

-----

)

)