Bonjour à tous,

Je suis actuellement en train de designer une carte électronique qui embarque un MCU (STM32) et j'utilise un quartz externe 8MHz comme source pour l'horloge. Comme la plupart des circuits numérique, la topologie utilisée de type "Pierce" avec un inverseur en parallèle a une résistance de feedback, auquel on rajout un quartz et des capa. Après avoir calculé et sourcé mes composants, me voici dans la phase de routage.

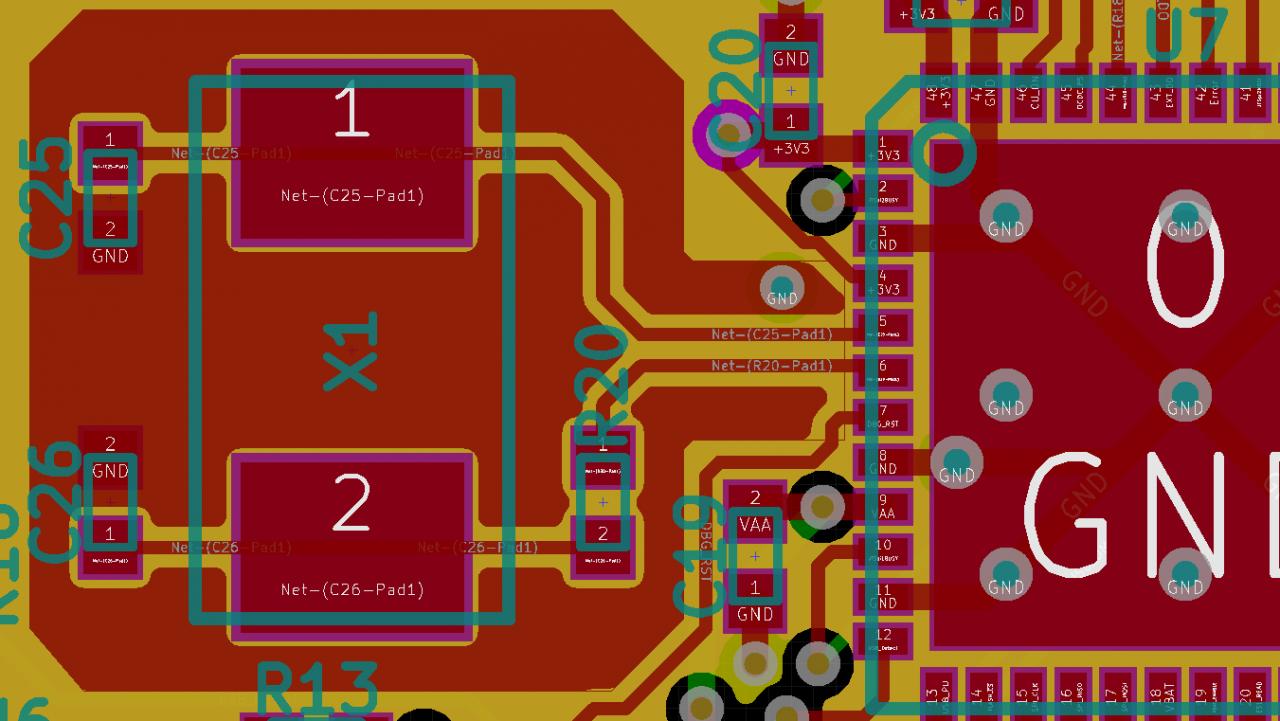

Après avoir lu pleins de note d'application, de forum et j'en passe, je me tourne vers la communauté de FS pour discuter de mon layout de l'oscillateur que voici :

Le PCB est un 4 couches :

top : signal

in1 : GND

in2 : VCC

bot : signal

A votre avis dois-je détourer le GND sur la couche top en dessous du quartz ?

Est ce que je dois aussi détourer le GND in1 et VCC in2 dessous l'oscillateur ?

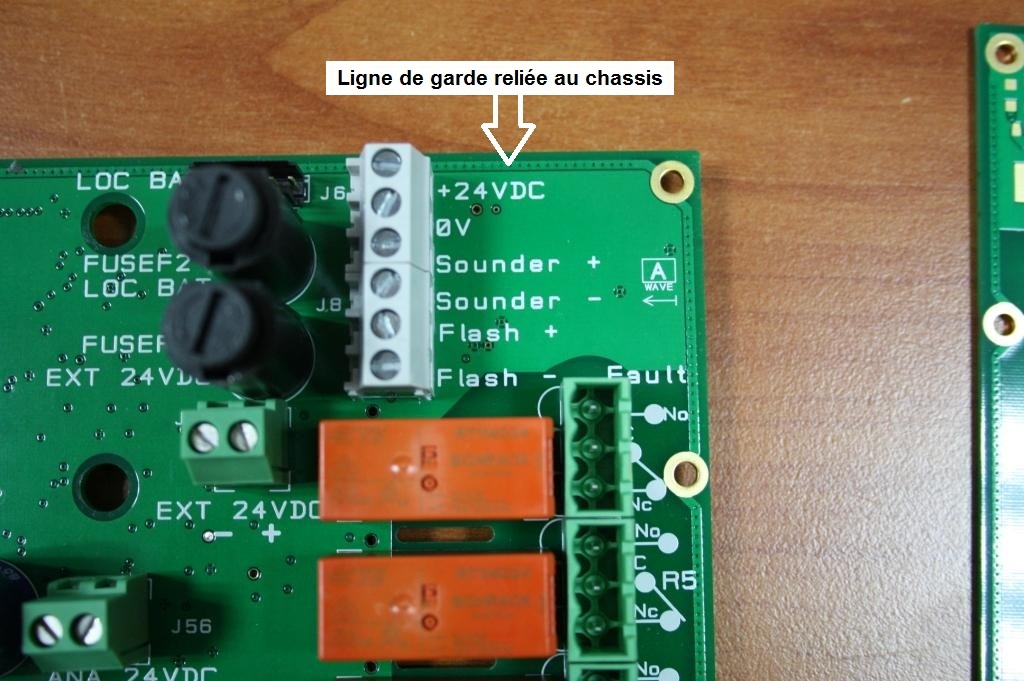

Est-ce que le design du "guard ring" est OK ?

J'ai déjà réalisé plusieurs cartes avec des quartz sans me poser ces questions et l'oscillateur à toujours démarré. La seul contrainte était la proximité avec le MCU.

Meilleures salutations

-----