Bonjour à tous les membres du forum,

Je suis actuellement rattaché en tant que stagiaire ingénieur à un projet pour le développement dune solution PCI Express « host » sur une cible FPGA Arria 10.

Après quelques jours dinvestigations, de recherches sur internet et plusieurs passées le nez dans les bouquins, je me suis familiarisé avec les spécifications de la norme PCI Express.

Ces mêmes recherches mont permis de me faire une vue densemble sur ce qui se fait en matière de solution PCI Express sur une cible FPGA.

La topologie traditionnelle, ou tout du moins celle qui est la plus mise en avant dans la littérature, est simplifiée comme suit :

FPGA Device -> PCI Express bloc -> Connecteur PCI Express -> Bus PCI Express -> Connecteur PCI Express -> Carte mère ordinateur -> CPU host

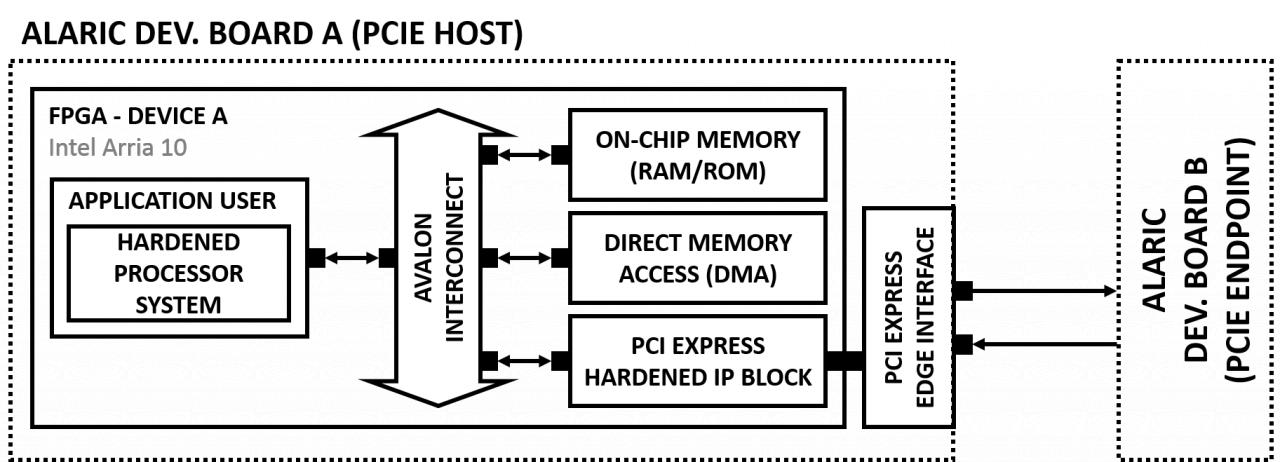

Dans sa finalité, ma mission consiste à substituer la carte mère dordinateur ainsi que le CPU déporté par une solution implémentée directement sur une cible FPGA Arria 10.

Après mêtre renseigné sur les caractéristiques techniques de ce FPGA, je me suis appuyé sur le bloc PCI Express Hard-IP présent dans ses couches de silicium ainsi que sur son processeur embarqué.

Il y a encore plusieurs notions qui me paraissent floues et qui demande une mise au point, notamment en ce qui concerne larchitecture nécessaire à limplémentation dune telle solution (On-Chip memory, DMA, MSI etc ).

Cette piste parait-elle faisable ? Auriez vous des conseils à me transmettre en ce qui concerne les périphériques indispensables pour la mise en place dune solution PCI Express ?

Je vous remercie,

-----