Bonjour a tous,

j'ai commencer a lire le cours sur le bus i2c, mais j'ai pas compris le signal sda sur le schémas suivant, est ce que quelqu'un peut me l'expliquer.

Cordialement

-----

Bonjour a tous,

j'ai commencer a lire le cours sur le bus i2c, mais j'ai pas compris le signal sda sur le schémas suivant, est ce que quelqu'un peut me l'expliquer.

Cordialement

Bonjour,

qu'est-ce que vous n'avez pas compris exactement?

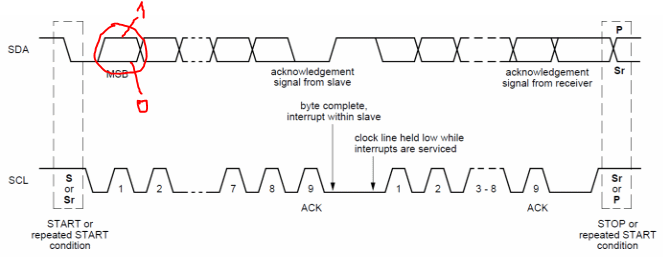

Pour initier un start il faut que la ligne SDA passe à 0, une fois cette condition détectée et validée la ligne SCL cadence l'horloge qui validera chaque bit transféré, selon un timing définit.

Ce que j'ai pas compris est comment le signal sda passe a '1' et rest a '0' em même temps

ça veut simplement dire que SDA peut prendre la valeur 1 OU 0

valeur qui sera lue quand SDL = 1

[b]le bon sens est un fardeau, car il faut s'entendre avec ceux qui ne l'ont pas [/b]

Il n'est pas "en même temps" à 1 et 0.

Il faut changer l'état de la ligne SDA qui était à 1 en la passant à 0 pendant que SCL est à 1 pour initier une condition de START.

Sur le signal vous voyez bien qu'il y a une transition (un front descendant).

Vous voyer sur l'image aprés la condition de départ le signal sda passe a 1 mais aussi il est a 0 la ou il ya D7 mais encore dans les autres D6,D5...

bonsoir , je ne vois pas la même chose .

Ok j'ai compris.

le fait que la data (le bit) puisse prendre un état 0 ou 1 fait que l'on représente de cette manière la data, une espèce de trapèze.

Voici un exemple réel relevé à l'oscillo:

on y voit les 9 coups d'horloge et le bit 1 qui vaut 1 soit un octet valant <B7~B0> : 00000010.

Le neuvième coup d'horloge est le NACK (not acknowledge)