Bonjour,

je dois "scanner" 256 entrées logiques le plus rapidement possible (modification de console d'orgue à tuyaux).

je ne peux pas utiliser des registres à décalage et une liaison SPI car je veux minimiser le temps de scrutation.(réduction de la latence au maximum)

je ne peux pas utiliser un système a matrice non plus.

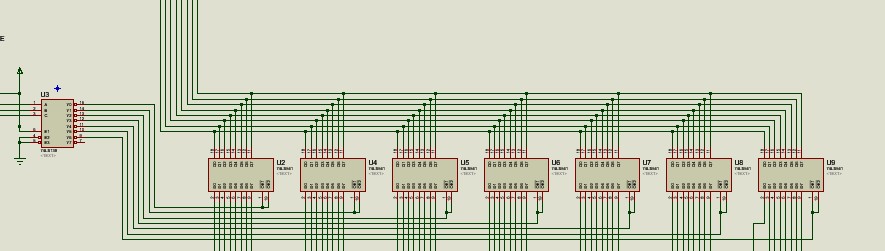

je pense utiliser des 74HC540. Sur les 8 entrées de chaque 74HC540 seront connectés des capteurs a effet hall détectant la position de la touche. les huit sorties de chaque CI formeront un bus de "data" qui seront sur le port D d'un pic.

je vais donc avoir 256/8 soit 32 74HC540 dont les sorties vont être en parallèle.

sachant qu'il n'y aura qu'un seul 74hc540 qui sera "activé" a la fois par la validation des entrée OE1 et OE2, et que les autres seront en sorties haute impédance, est ce raisonnable de mettre ces 32 sorties de circuit en parallèle ?

merci pour votre avis !

un bout de schéma avec seulement 7 circuits.

-----