Bonjour,

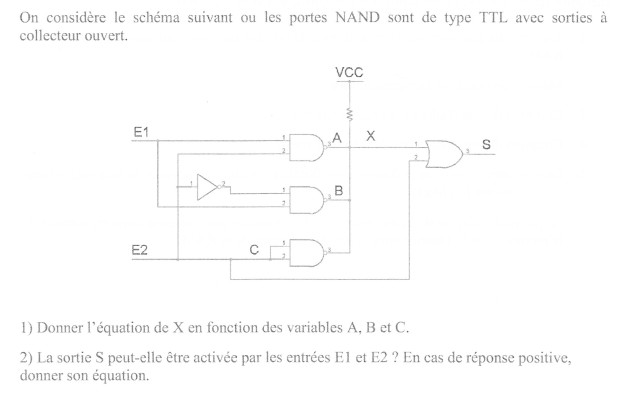

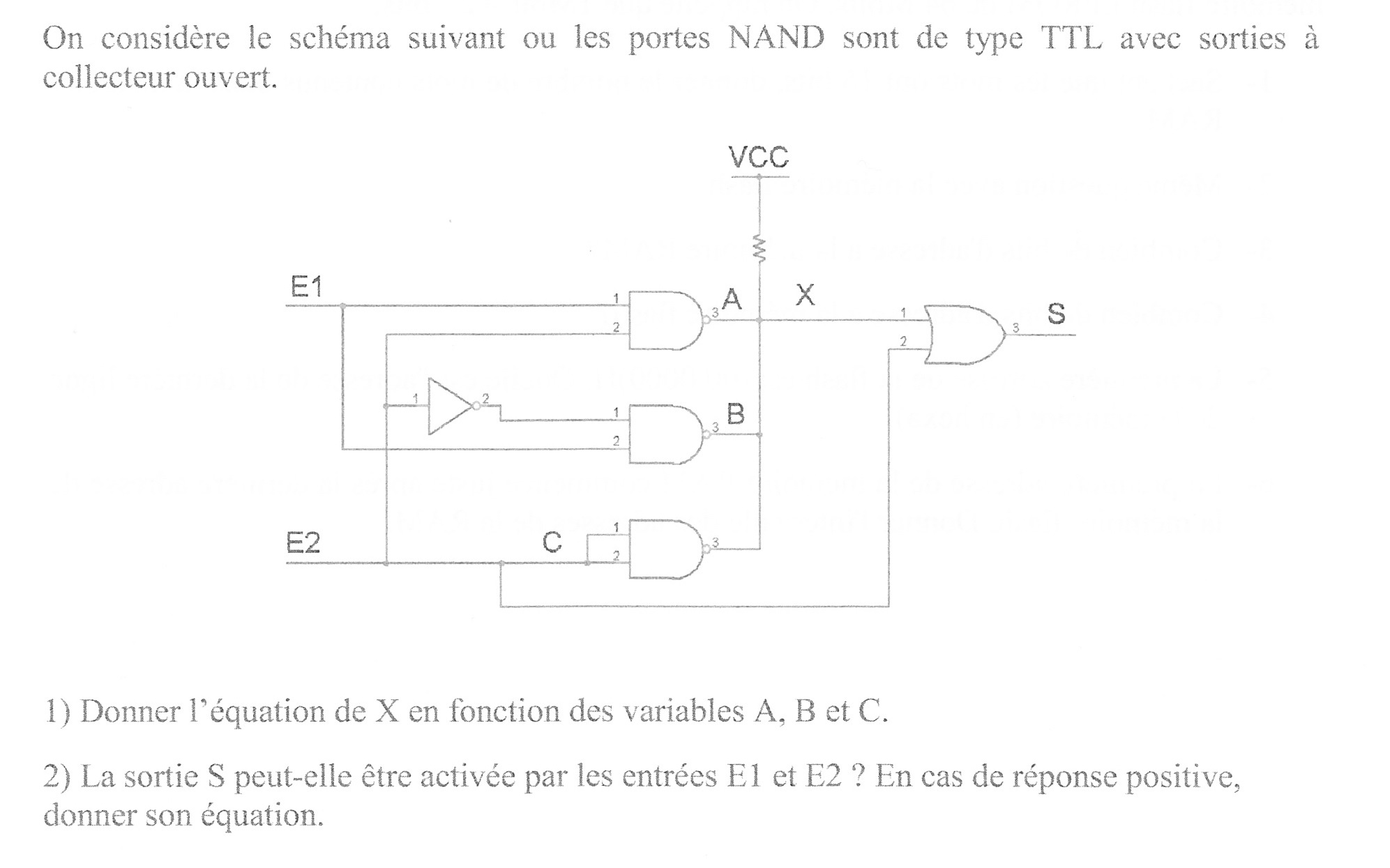

Pouvez-vous m'aider à comprendre la réalisation de cet exercice. C'est la question 1 qui me pose problème :

1) Si j'en crois mon cours, les sorties des portes NON-ET doivent être à 0 pour bloquer les transistors (sortie à collecteur ouvert) et ainsi mettre X au niveau haut (X=1). Autrement dit toutes les entrées des portes NON-ET doivent être à 1.

Il suffit qu'au moins une seule sortie des portes NON-ET soit à 1 pour qu'un des transistors soit passant et donc que X soit au niveau bas (X=0).

Alors moi je suis tenté de dire que X=A/.B/.C

En effet X=1 que lorsque les sorties sont à 0 donc A=0, B=0 et C=1 (C étant situé avant la porte NON-ET).

Qu'en pensez-vous ?

Merci.

-----