Bonjour,

je me posais une question sur les circuits synchrones.

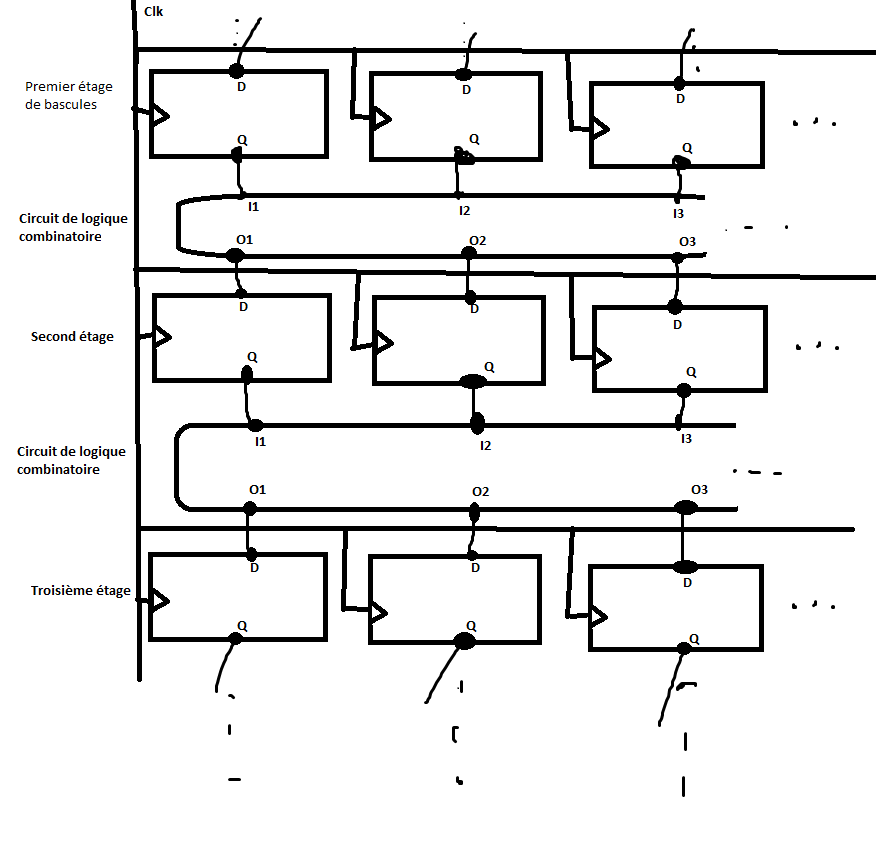

Si j'ai bien compris, un modèle de ces circuits pourrait être celui-là :

(excusez le schéma fait à l'arrache sur paint).

Les changements d'état d'un étage sont contrôlés par les états de l'étage précédent et ont lieu lors d'un front d'horloge.

Ce que je me demandais, c'est si c'était une problème que les états d'un étage changent pile en même temps que ceux de l'étage suivant, bien que ce soit le principe. Je m'explique : la sortie d'une bascule A est branchée sur l'entrée D de la bascule B. Sur le front d'horloge, la bascule A change d'état. Cela veut dire que l'entrée D de B commute pile en même temps (ou juste plus tard) que l'horloge.

Sauf erreur, dans ce cas, la bascule B aura un comportement indéterminé.

J'ai l'impression que la solution se trouve dans le choix approprié du temps de propagation du signal dans les bascules (le juste plus tard d'avant), et le "hold-time" de D. Mais cela veut dire que si je change une bascule, le circuit pourrait ne plus marcher...

Où est l'erreur ?

Merci !

-----