Bonjour à tous,

Je fais appel à vous pour discuter d'un problème que je rencontre lors de la programmation de mon pic16.

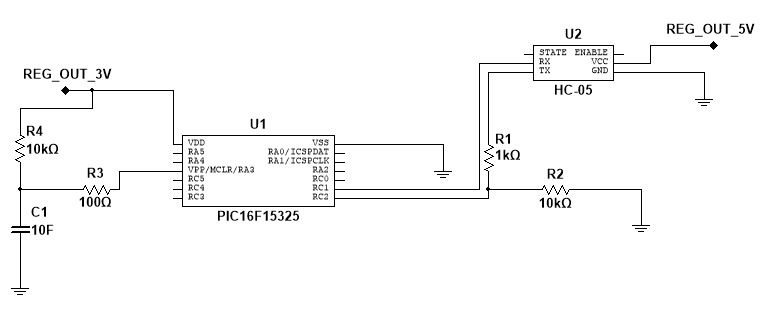

En effet, celui-ci ne démarre pas automatiquement. Il semblerait que je doive le maintenir constamment connecté à mon Pickit 3 (programmeur) pour que l'horloge se mette en marche. J'ai remarqué que lorsque je relie une masse ou un connecteur tel que l'ICSPDAT, le pic16 démarre. (Visualisation de la CLK sur la broche CLKOUT)

Auriez-vous des idées ou des suggestions à ce sujet ?

Toute aide serait grandement appréciée !

Merci beaucoup !!

Ci-contre, voici mon code :

Code:/ CONFIG1 #pragma config FEXTOSC = OFF // External Oscillator mode selection bits->Oscillator not enabled #pragma config RSTOSC = HFINTPLL // Power-up default value for COSC bits->HFINTOSC with 2x PLL, with OSCFRQ = 16 MHz and CDIV = 1:1 (FOSC = 32 MHz) #pragma config CLKOUTEN = ON // Clock Out Enable bit->CLKOUT function is enabled; FOSC/4 clock appears at OSC2 #pragma config CSWEN = ON // Clock Switch Enable bit->Writing to NOSC and NDIV is allowed #pragma config FCMEN = ON // Fail-Safe Clock Monitor Enable bit->FSCM timer enabled // CONFIG2 #pragma config MCLRE = ON // Master Clear Enable bit->MCLR pin is Master Clear function #pragma config PWRTE = OFF // Power-up Timer Enable bit->PWRT disabled #pragma config LPBOREN = OFF // Low-Power BOR enable bit->ULPBOR disabled #pragma config BOREN = OFF // Brown-out reset enable bits->Brown-out reset disabled #pragma config BORV = LO // Brown-out Reset Voltage Selection->Brown-out Reset Voltage (VBOR) set to 1.9V on LF, and 2.45V on F Devices #pragma config ZCD = OFF // Zero-cross detect disable->Zero-cross detect circuit is disabled at POR. #pragma config PPS1WAY = ON // Peripheral Pin Select one-way control->The PPSLOCK bit can be cleared and set only once in software #pragma config STVREN = ON // Stack Overflow/Underflow Reset Enable bit->Stack Overflow or Underflow will cause a reset // CONFIG3 #pragma config WDTCPS = WDTCPS_31 // WDT Period Select bits->Divider ratio 1:65536; software control of WDTPS #pragma config WDTE = OFF // WDT operating mode->WDT Disabled, SWDTEN is ignored #pragma config WDTCWS = WDTCWS_7 // WDT Window Select bits->window always open (100%); software control; keyed access not required #pragma config WDTCCS = SC // WDT input clock selector->Software Control // CONFIG4 #pragma config BBSIZE = BB512 // ->512 words boot block size #pragma config BBEN = OFF // ->Boot Block disabled #pragma config SAFEN = OFF // ->SAF disabled #pragma config WRTAPP = OFF // ->Application Block not write protected #pragma config WRTB = OFF // ->Boot Block not write protected #pragma config WRTC = OFF // ->Configuration Register not write protected #pragma config WRTSAF = OFF // ->SAF not write protected #pragma config LVP = OFF // Low Voltage Programming Enable bit->High Voltage on MCLR/Vpp must be used for programming // CONFIG5 #pragma config CP = OFF // UserNVM Program memory code protection bit->UserNVM code protection disabled

-----