Bonsoir,

L'idée pour loscillateur unique c'était d'avoir la même source pour tous les VDP, et aussi réduire le cout, un quartz coute moins que 4

Sachant que la synchro se fera par les signaux de synchro du VDP "maître" qui vont servir à synchroniser les VDP "esclave" via leur entrée /HRESET et /VRESET.

Avez vous un schéma pour générer un signal au moment de la synchro (Synchronyze signal) page 4 du fichier Synchro_V99x8?

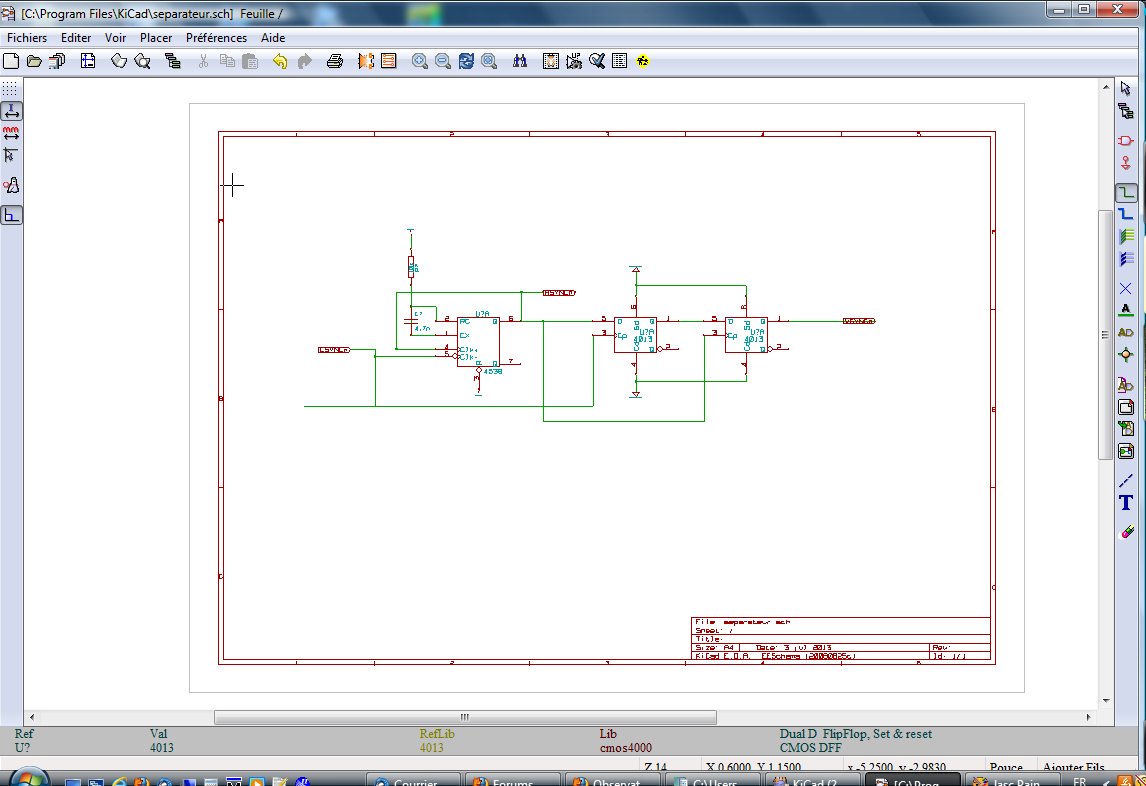

J'avais dans l'idée d'utiliser du 74LS123 ou du 4538. l'idée c'est d'utilisé la spécificité du temps "long" à l'état bas de CSYNC pour détecter la phase "synchronyze signal". En gros sur un front descendant on arme un monostable pour un temps >4,66µs et on fait un NAND entre la sortie /Q du monostable et CSYNC pour armer un second monostable qui nous génère un top de 3x2,98µs sur /VRESET.

En suite j'ai pas encore de solution pour balancer un top sur /HRESET en ligne 6 (la 7eme vu qu'on compte à partir de 0) quand le VDP "maître" génère son top ligne sur /HSYNC.

Si vous pouviez m'éclairer parce que pour le moment je sèche.

Merci pour votre temps.

-----