Concernant R9 - R12 :

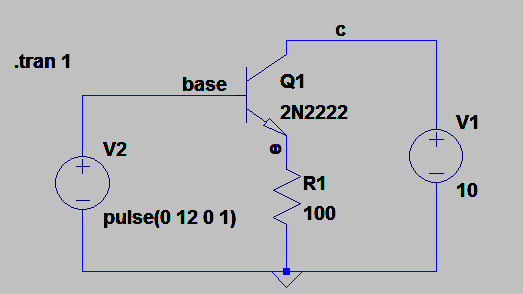

La tension entre base et émetteur d'un transistor bipolaire est quasi-constante (c'est une diode) égale à ~0,7V. Lorsque la commande est à un potentiel donné, il faut que le potentiel de la base ou bien celui de l'émetteur soit libre :

- dans le montage émetteur commun (Q3) : le potentiel de l'émetteur est fixe égal à 0V, le potentiel de la base est "libre" grace à la résistance R10 (si tu branches directement la base sur la sortie de l'AOP, l'AOP essaye de mettre un potentiel de 12V (par exemple) tandis que la diode base-émetteur essaye de mettre un potentiel de 0,7V => le courant de base n'est pas limité => ya un problème).

- dans le montage collecteur commun (Q4) : le potentiel du collecteur est fixe égal à Vcc, le potentiel de l'émetteur est libre, tu peux donc choisir le potentiel de la base, par exemple en la reliant directement en sortie de l'AOP.

-----

).

).

).

).

ost plus en amont).

ost plus en amont).