Bonjour,

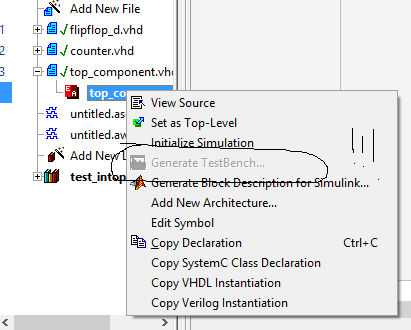

Débutant en VHDL, j'ai voulu tenter de faire fonctionner un compteur à N bits que j'ai trouvé sur le site d'une université. Pour cela, j'ai utilisé le logiciel Active HDL mais malheureusement je n'ai pas réussi à obtenir le résultat.

Le code que j'ai utilisé est le suivant :

Je devais donc obtenir le résultat suivant :Code:---------------------------------------------------- -- VHDL code for n-bit counter (ESD figure 2.6) -- by Weijun Zhang, 04/2001 -- -- this is the behavior description of n-bit counter -- another way can be used is FSM model. ---------------------------------------------------- library ieee ; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; ---------------------------------------------------- entity counter is generic(n: natural :=2); port( clock: in std_logic; clear: in std_logic; count: in std_logic; Q: out std_logic_vector(n-1 downto 0) ); end counter; ---------------------------------------------------- architecture behv of counter is signal Pre_Q: std_logic_vector(n-1 downto 0); begin -- behavior describe the counter process(clock, count, clear) begin if clear = '1' then Pre_Q <= Pre_Q - Pre_Q; elsif (clock='1' and clock'event) then if count = '1' then Pre_Q <= Pre_Q + 1; end if; end if; end process; -- concurrent assignment statement Q <= Pre_Q; end behv; -----------------------------------------------------

http://esd.cs.ucr.edu/labs/tutorial/counter.jpg

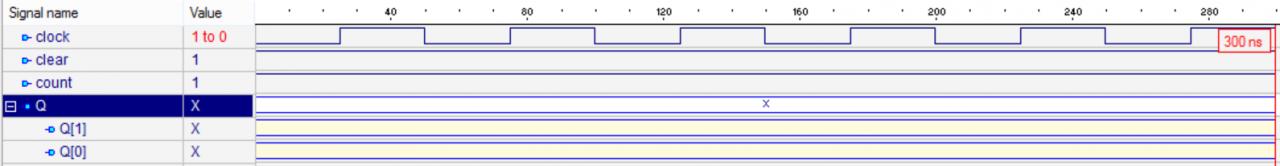

Pour faire mes simulations, j'ai utilisé une horloge de 20 Mhz, j'ai initialisé clear et count à 1 pour tester. Normalement, je devais avoir pour la sortie Q 0 tout le temps (car clear à 1) mais j'obtiens un "X"

J'ai beau chercher l'erreur, je ne trouve pas d'où elle vient

Voici le résultat que j'obtiens :

Savez-vous d'où peut provenir mon erreur ?

Je vous remercie d'avance pour votre précieuse aide

-----