Bonjour,

Je suis une débutante dans la programmation vhdl, pour commencer j'allumais des leds et je faisais de la logique combinatoire pour me familiariser avec ce langague mais il m'est demander de faire des filtre (passe_bas, passe_haut, passe_band,RIF...) je n'ai aucune idée sur comment m'y prendresi quelqu'un a deja fait cela ou a deja croiser un site qui parle de ca, je suis preneuse de tous ce que vous avez sur la programmation des filtres en VHDL .

Merci beaucoup de votre future aide

-----

n'est autre une filtre à réponse impulsionnelle infini (IIR)!

n'est autre une filtre à réponse impulsionnelle infini (IIR)!

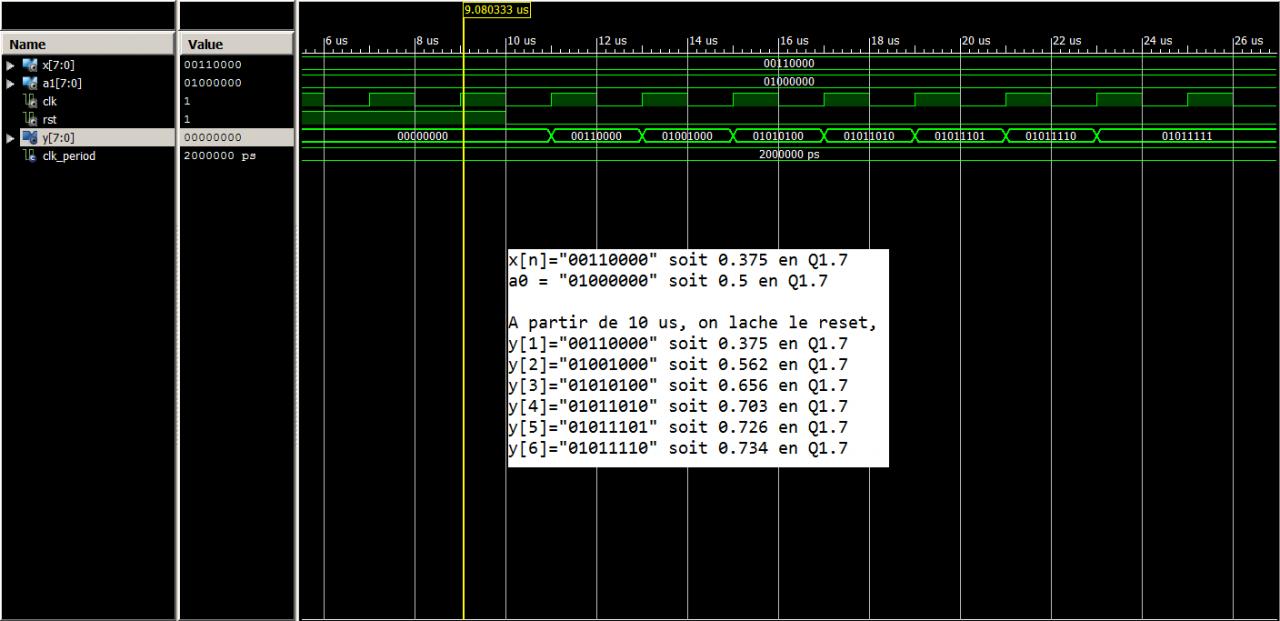

, ce n'est pas très utile, mais ce n'est pas ce qui est codé car x étendu = x(7)&X&"0000000" le & étant la concaténation Xn est donc subrepticement divisé par 2; On retombe alors sur la forme simple Yn = Xn/2+(Yn-1)/2 filtre ayant un gain de un ce qui est prudent si l'on ne veut pas se faire c..r à gérer la virgule au delà du raisonnable.

, ce n'est pas très utile, mais ce n'est pas ce qui est codé car x étendu = x(7)&X&"0000000" le & étant la concaténation Xn est donc subrepticement divisé par 2; On retombe alors sur la forme simple Yn = Xn/2+(Yn-1)/2 filtre ayant un gain de un ce qui est prudent si l'on ne veut pas se faire c..r à gérer la virgule au delà du raisonnable. ) bref je vous le joins et j'attends vos commentaires

) bref je vous le joins et j'attends vos commentaires  svp

svp

, j'ai changé le programme de la dernière fois afin d’implémenter ce filtre là y[n]=x[n]+y[n-1]/2, euuuh juste une question qui a peut être l'aire bête, dites moi, c'est à quel moment on donne la fréquence de coupure d'un filtre passe bas

, j'ai changé le programme de la dernière fois afin d’implémenter ce filtre là y[n]=x[n]+y[n-1]/2, euuuh juste une question qui a peut être l'aire bête, dites moi, c'est à quel moment on donne la fréquence de coupure d'un filtre passe bas