Bonjour, je suis novice en electronique numerique, je suis tombé sur un exercice que j'ai du mal à comprendre. Je voulais savoir si mon raisonnement est juste.

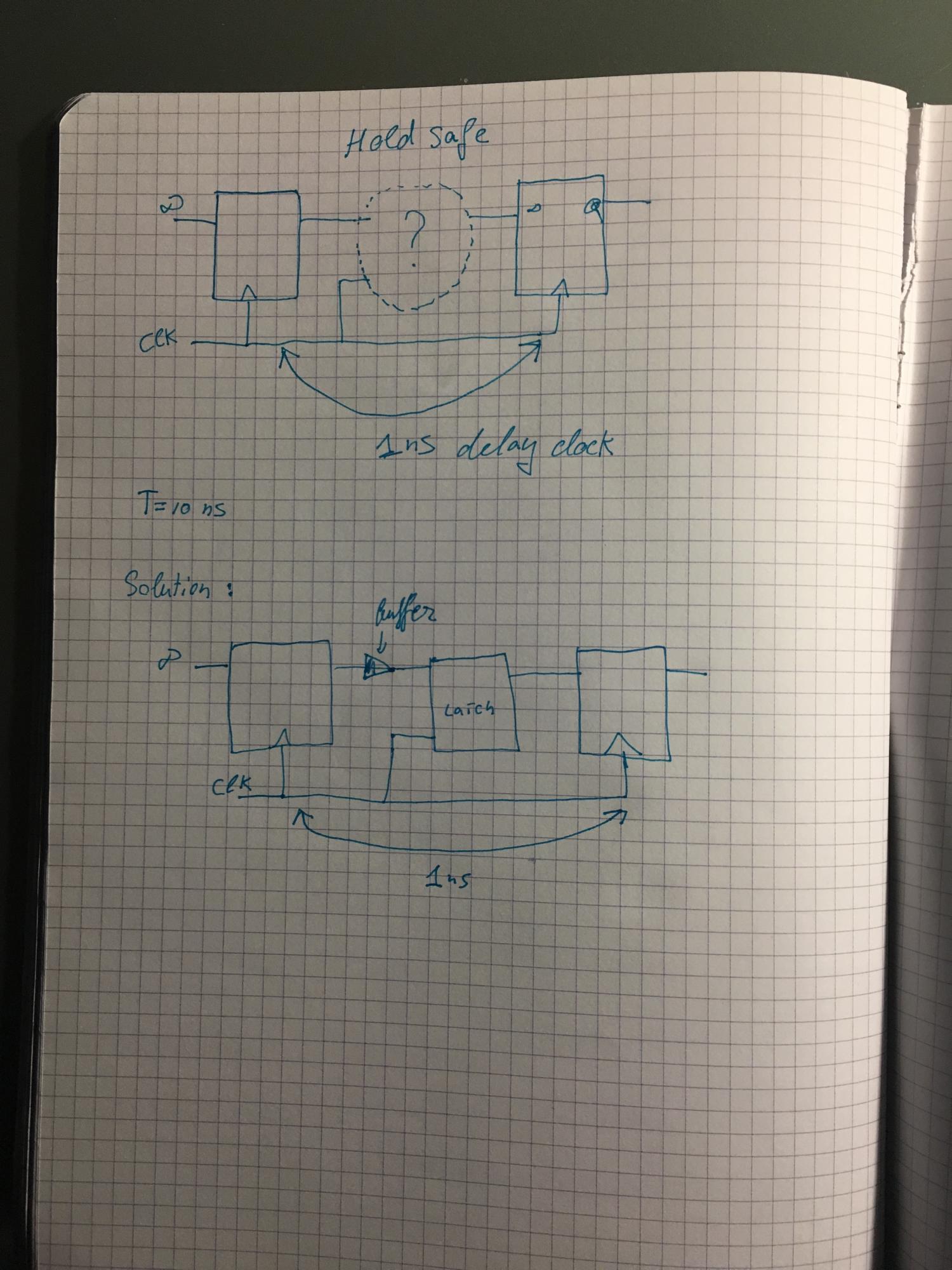

Voir la photo ci jointe. Si par example la période de l'horloge est de 10 ns, et le delay de l'horloge en arrivant à la 2eme flip flop est 1ns, quel type de circuit peut on rajouter entre les deux flip flop pour avoir un "Hold safe value" entre la sortie de la premier bascule et l'entrée de la deuxième en tenant compte du délai de l'horloge vers la 2eme flip flop.

Une des solutions j'ai pense mettre un buffer à la sortie du 1er flip flop et mettre une D latch entre la 1er flip flop et la 2eme, avec l'horloge sur l'entrée ENABLE de la latch. Je ne suis pas sur de mon raisonnement. Car une autre idée que jai eu cest juste de mettre un buffer pour la 1er bascule (clock) pour rééquilibrer larbre dhorloge.

Je vous remercie pour la cooperation

-----