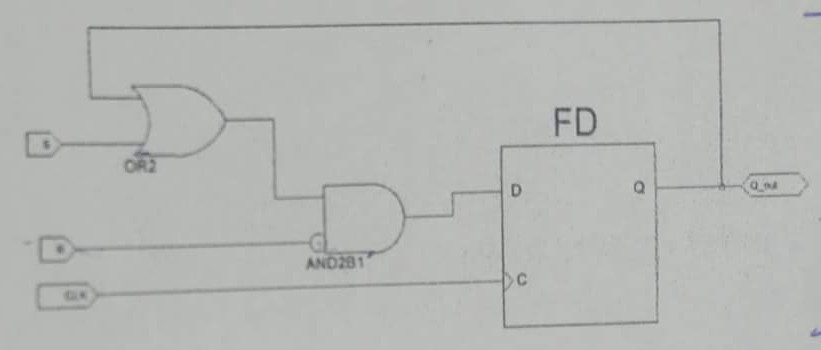

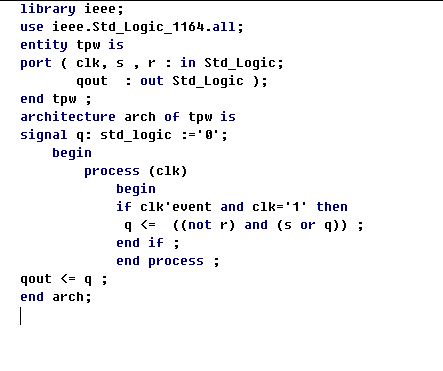

Voici in code que j'ai fais concernant un circuitCode:library ieee; use ieee.Std_Logic_1164.all; entity tp4_4 is port ( clk, S , R : in Std_Logic; Qout : out Std_Logic ); end tp4_4; architecture archi of tp4_4 is signal D : std_logic ; begin P1: process (clk) begin if clk='1' and clk'event then D <=(( not R) and (S and qout); qout <= D; end if ; end process ; end archi;

-----