Bonjour,

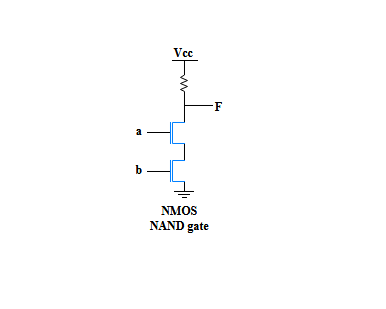

Est-ce que l'on pourrait m'expliquer comment fonctionne un NMOS NAND car je n'arrive pas à comprendre malgré les nombreuses heures de recherches sur internet.

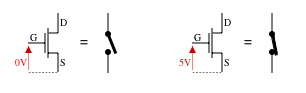

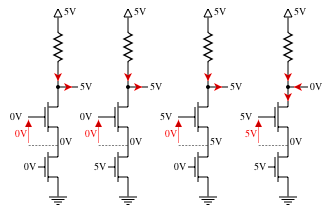

Ce que je ne comprends pas c'est comment passe le courant en fait ? on voit qu'il y a une sortie F qui est juste avant le collecteur et que tout en bas il y a apparemment une mise à la terre donc pour moi le courant qui passe via le collecteur dans la résistance devrait normalement passé directement à la sortie F et peut importe si a et b sont ouvert ou fermé non décidément je ne comprends pas normalement la sortie devrait être en bas non ce qui permettrai d'avoir les portes a et b qui pourrait jouer leurs rôles. Ici sur ce schéma les portes sont après l'arrivé des électrons donc sa ne peut pas fonctionner et pourtant sa fonctionne je comprends pas

?

Voici une image :

-----