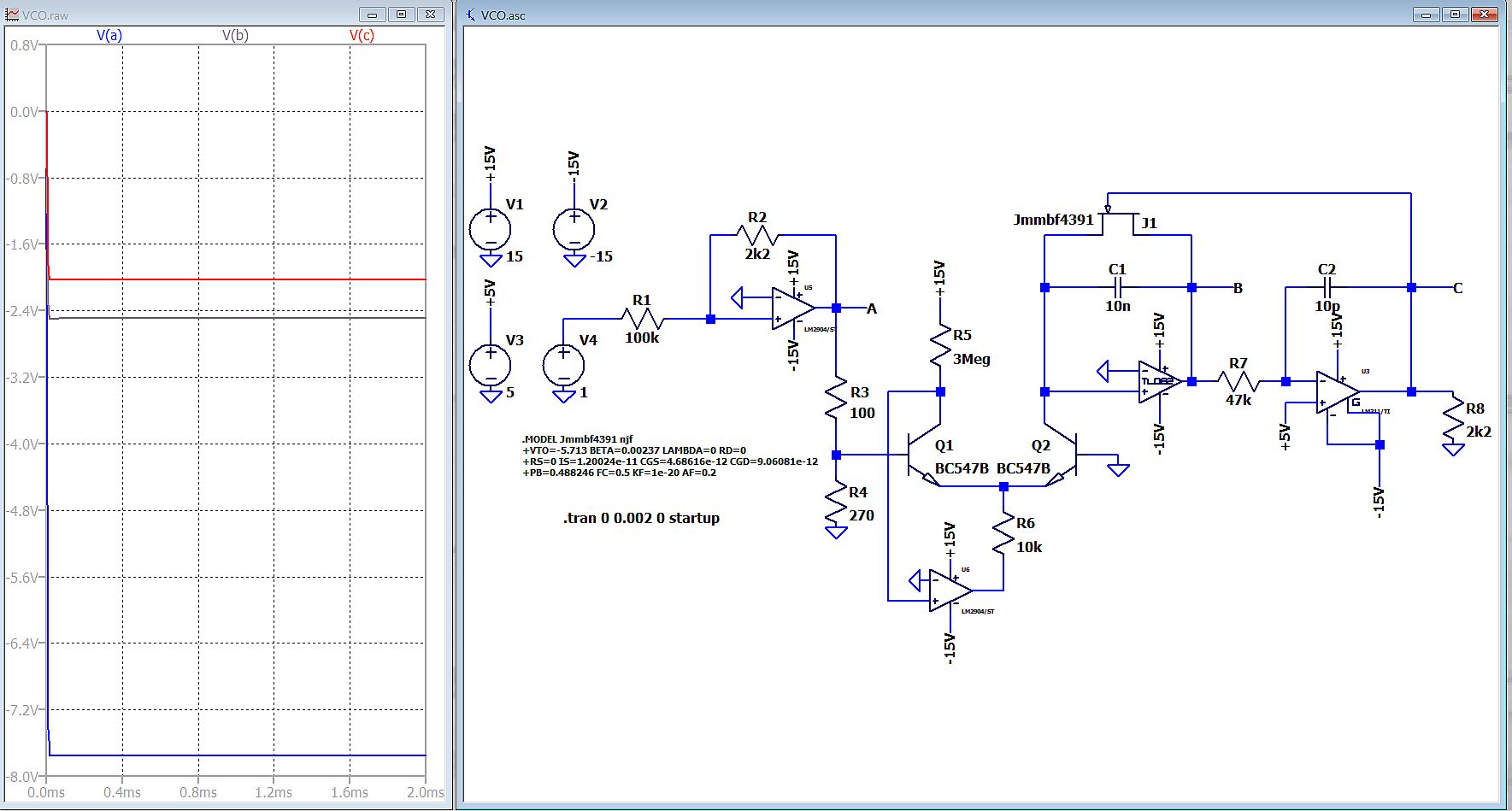

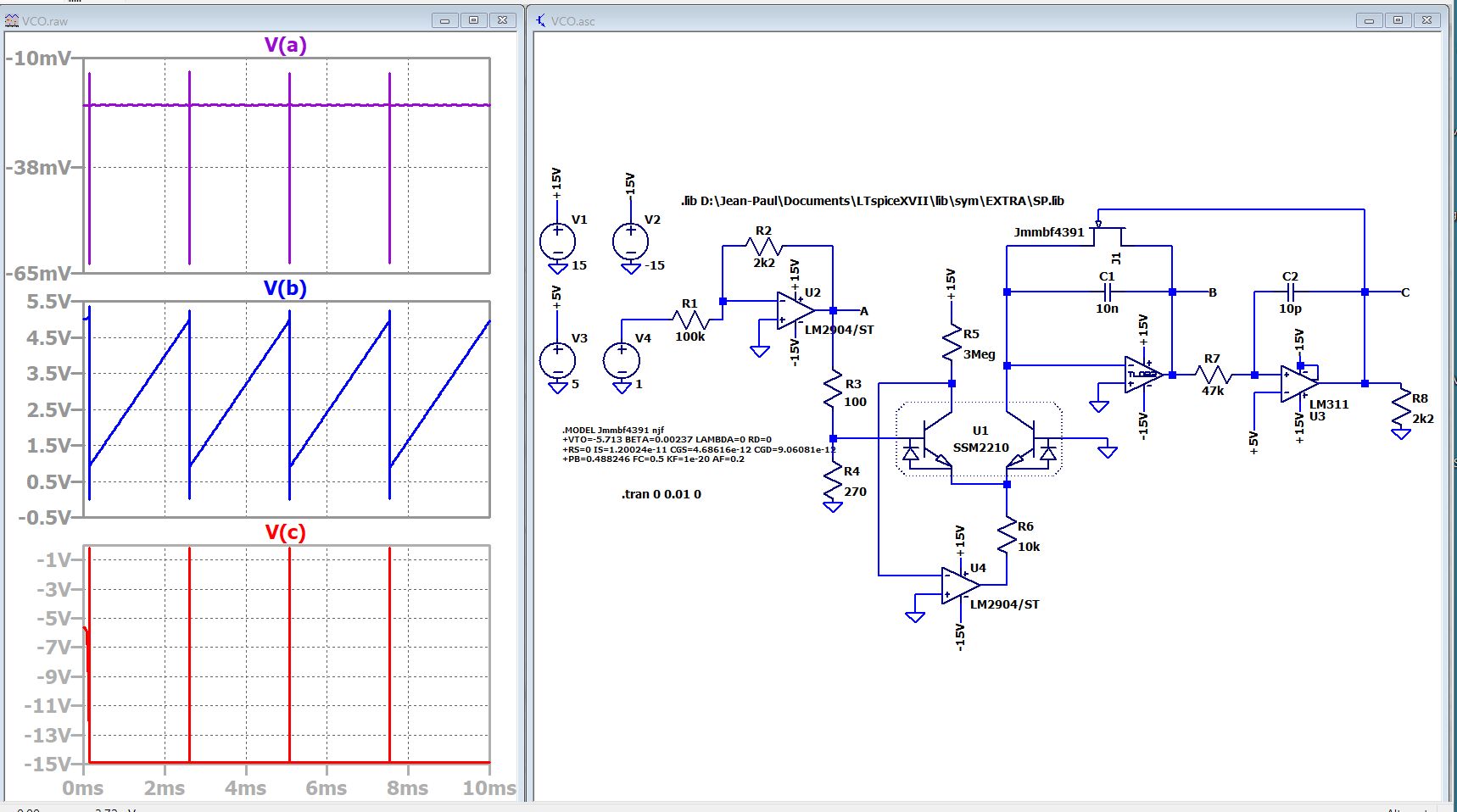

Bonsoir, je n'arrive pas à simuler mon circuit (c'est un VCO pour synthé).

Untitled.jpg

à chaque fois que je lance la simulation, le programme tourne à l'infini et ne m'affiche pas la fenêtre de l'oscillogramme.

Svp, si quelqu'un a une idée, ce serait sympa.

-----