Bonjour,

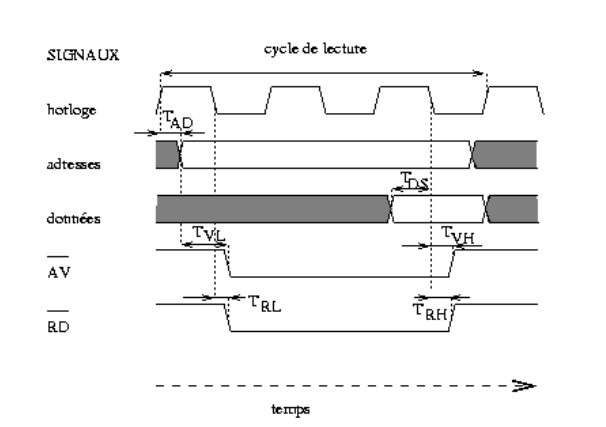

Voici un chronogramme de lecture synchrone sur un bus :

Je ne comprend pas ce que représente "AV" et "BD" (surmontés d'une barre).

Quelqu'un peut-i m'expliquer ?

J'aimerais également savoir ce qui change dans le cas d'un chronogramme d'écriture synchrone sur un bus ?

Quelqu'un peut-il m'aider ?

Merci d'avance !

-----

et

et