Bonjour,

Je solicite votre aide car après une semaine de creusage de tête, je tourne encore et toujours en rond.

Je voudrai develloper un banc de test pour le cablage de shunts sur une prise.

Explication:

Des shunts sont disposés entre deux contacts d'une prise et j'aimerai develloper une carte electronique qui vérifie que ces shunts est disposé entre les bon contacts de cette prise. Il y a 50 shunt differents sur differents contacts

prise.GIF

Au debut j'ai simplement pensé faire:

Sans titre.JPG

Mais dans ce cas la, on peut brancher les shunts n'importe comment et le temoin s'alume.

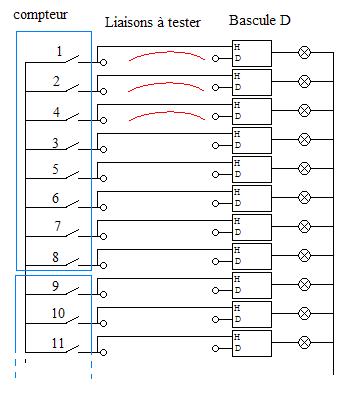

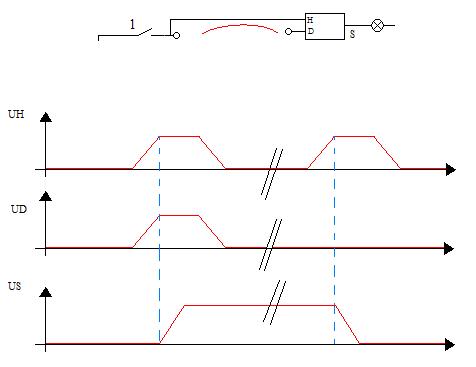

Alors je me suis dit qu'il fallait les tester un par un d'ou l'utilisation d'un registre à decalage ou un compteur decimal qui ballayerais à haute fréquence la continuité entre les differents contacts.

rg.JPG

Mais les leds recoivent trop peut d'energie car elles sont allimentées avec un raport cyclique 1/50.

J'ai ensuite voulu garder en memoire la derniere valeur mesurée avec une bascule D mais je n'ai pas réussie à trouver la solution.

Je suis maintenant partie sur l'utilisation d'un PIC et de registre à decalage afin de d'afficher les érreurs de cablage sur un afficheur plutot qu'avec des leds.

Mais je dois avouer que les registres a décalage serialisateur et déserialisateur sont un mystère pour moi, et je ne trouve pas comment les cascader. j'ai eu beau écumer les forums, je ne trouve rien. je ne cherche peut étre pas au bon endroit.

J'ai pensé au 74HC164 et au 74HC164 mais je serai obligé de rajouter une porte inverseuse non?

Aujourd'hui j'en suis là, et je suis perdu...

shema.JPG

-----