Bonjour à tous,

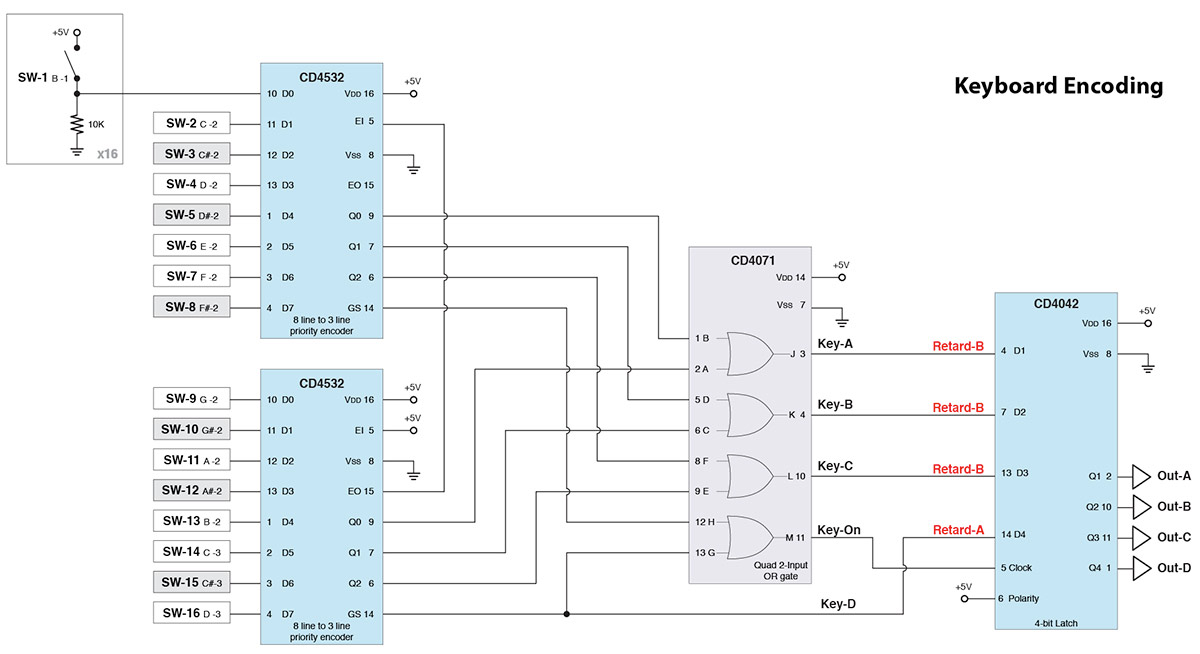

je reviens aujourd'hui avec le schéma d'encodage d'un clavier composé de 16 switchs tactiles.

Nous voyons ici que le clavier est encodé à l'aide de deux CD4532 et d'un CD4071. Le schéma est tiré du datasheet du CD4532.

Le CD4532 est un "8 x 3 line priority encoder":

http://www.mouser.com/ds/2/405/cd4532b-439725.pdf

Le CD4071 est un classique "4 x OR gates"

http://www.mouser.com/ds/2/405/cd4071b-441609.pdf

En sortie j'ai rajouté un verrou 4 bits , un CD4042, qui permet de "garder en mémoire" le dernier switch actionné.

http://www.mouser.com/ds/2/405/cd4042b-406629.pdf

En théorie ça marche bien sauf qu'en pratique le circuit ne fonctionne pas pour cause de retard des signaux.

En effet la sortie "Key-D" est légèrement en avance par rapport aux autres signaux (Key-A, Key-B, Key-C et Key-On) ce qui fait que cette valeur n'est pas prise en compte quand le verrou se referme.

Cela est dut au fait que le signal Key-D n'est pas retardé par le CD4071 comme les autres signaux. Si je comprends bien le datasheet, ce retard va de 100 à 200 ns pour une alimentation 5V.

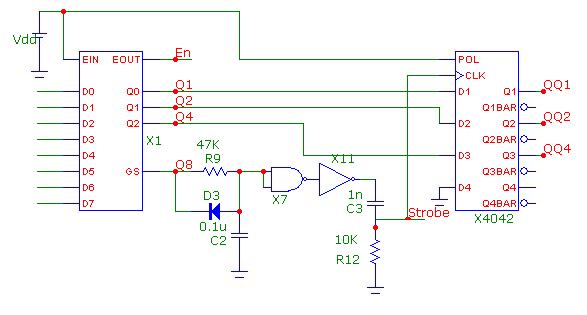

1-Ma première question est la suivante: Puisque qu'il faut retarder le signal Key-D (Retard A) quelle est la méthode la plus élégante pour le faire ?

- Pour le moment j'utilise une paire d'inverseur logique (CD4069)en série, ça fonctionne correctement.

http://www.mouser.com/ds/2/405/cd4069ub-452619.pdf

- J'imagine qu'un simple circuit condensateur/résistance (par exemple 0,47uF et 10K) devrait aussi fonctionner.

-Peut-être même qu'un simple "buffer" CD4050 pourrait faire l'affaire.

http://www.mouser.com/ds/2/405/cd4050b-452617.pdf

2-Même si ce circuit fonctionne mieux, cela n'est pas toujours suffisant et des erreurs apparaissent encore en sortie de verrou.

Ces erreur concernent la synchronisation de Key-On et Key-A, Key-B, Key C. En effet il faut s'assurer que les autres signaux sont encore actifs quand Key-On passe au niveau bas.

Ma deuxième question concerne donc le retard B.

Là encore pour ralentir les signaux Key-A, Key -B et Key-C par rapport à Key On, quelle serait la méthode la plus élégante parmi celles précédemment citées?

3-Enfin ma troisième question:

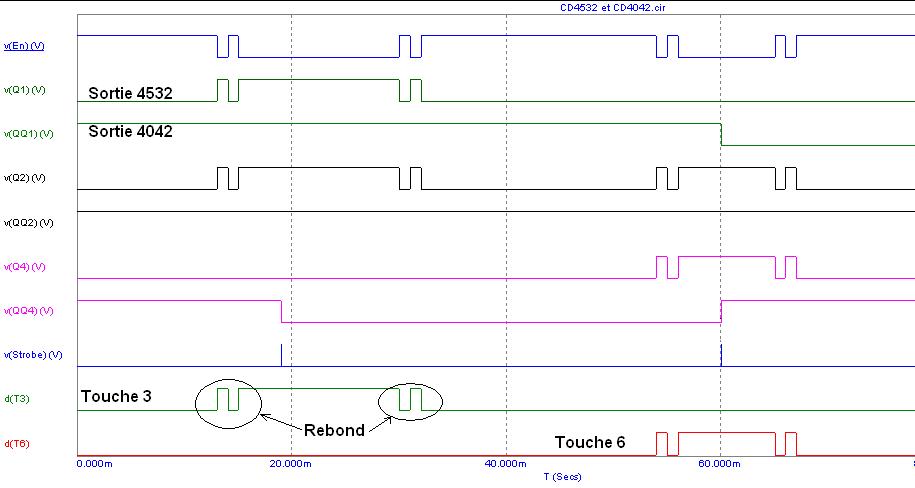

Vous remarquerez que je n'ai pas placé de condensateurs anti-rebond parallèlement aux 16 switchs d'entrée.

Cela parce que je considère que peu importe le rebond pourvu la valeur ai eu le temps d'être mise en mémoire dans le latch.

Cela vous paraît-il juste où il s'agit-il d'une mauvaise interprétation?

Merci par avance de vos réponses.

-----