Bonjour, je souhaite vous remercier d'avance pour le temps que vous prenez à lire ce post.

Je suis en DUT par apprentissage et j'ai un projet à faire en entreprise. Je suis un peu en difficulté.

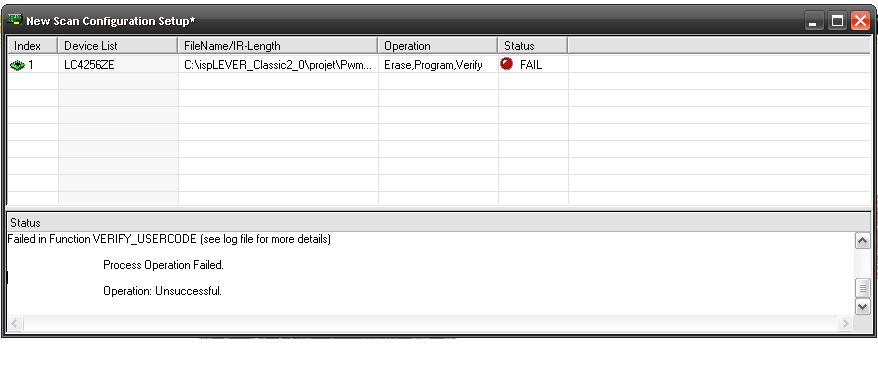

Je vais vous expliquer ma situation, je dois réaliser a un projet pour tester des matériels industrielle, dans ce projet je dois avoir une fréquence de 8Khz pour cela j'ai pris un oscillateur à quartz 4Mhz qui a été divisé avec le CD4040 en j'ai donc mes 8 Khz, je devais encore autres choses mais ça n'est pas un soucis, mon problème est qu'avec cette fréquence je dois faire varier le rapport cyclique pour cela j'utilise le kit d'évaluation "ispMACH 4256ZE" que je dois programmer avec le logiciel de chez lattice soit "ispLever" le soucis c'est que je ne suis pas très compétent en VHDL et je dois le programmer en VHDL je ne sais pas comment m'y prendre et puis j'ai des difficultés à utiliser "ispLever" ma question c'est comment faire pour varier le rapport cyclique ? J'ai déjà fais des recherche et je suis tombé sur ça :

Moi je veux que mon rapport cyclique soit varier de 0% a 100% par pas de 1 en utilisant la clock avec l'oscillateur et non la clock de l'ISP.Code:library ieee; use ieee.std_logic_1164.all; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity pwm is port ( clk: in std_logic; SW : in std_logic_vector (3 downto 0); --rapport cyclique (de 0 à 10) reset : in std_logic; GPIO_0 : out std_logic_vector(35 downto 0)); -- sortie end pwm; architecture behavior of pwm is signal cnt : std_logic_vector(3 downto 0) := "0000"; signal s : std_logic; begin process (clk,rst) begin if reset ='1' then s<=(others=>'0'); // Ici il n'y a pas un problème ??quand je compile cela m'adresse une erreur :sos: elsif (clk'event and clk='1') then if (cnt < SW) then s <='1'; --met la sortie à 1 jusqu'a else s <='0'; --la valeur du rapport cyclique end if; if (cnt >= "1001") then cnt<="0000"; --remet à 0 quand on a // Si je met "0010" à la place de "1001" sa fera un rapport cyclique par pas de 1? else cnt <= cnt + 1; -- compté jusqu'a 10 end if; end if; end process; GPIO_0(29) <= s; end behavior;

Je ne comprends pas trop comment faire et je comprend pas trop le programme, si quelqu'un peut me détailler plus clairement le programme et m'orienter sur comment débuter, ce serait avec grand plaisir que je prendrais en compte ces informations.

Au pire des cas je générerais ma PWM avec VHDL et le kit mais je ne vois pas du tout comment faire ça.

Je vous remercie encore une fois pour le temps que vous m'accordez.

-----