Bonsoir

Comment faire clignoter deux affichage 7 segment sur une carte Altera sous quartus ?

merci

-----

Bonsoir

Comment faire clignoter deux affichage 7 segment sur une carte Altera sous quartus ?

merci

Tu peux donner le schéma de branchement de tes afficheurs avec ta carte ?

voila c est ce que j ai fait

Sauf qu'on ne voit pas le branchement des afficheurs ???

Si tu as un affichage, tu as des afficheurs 7 segments (LED? LCD?) . Ils sont connectés comment sur ton circuit !

Je laisse tomber. Je pose une question, je voulais une réponse . Bye .Envoyé par daudet

Je veux le schéma filaire de tes afficheurs avec ton schéma !

Et bien tu donnes le bout de schéma de cette carte avec le circuit programmable et les afficheurs

Mais.mon affichage marche je l.ai deja tester et envoye mon projet sur la carte et ca a marqué OU ou FE sur les affichage 7 segment mais je voudrais que quand il y ait ecrit FE donc quand Sa est a 1 que ca clignote

Mais.si tu veut que je te redéssine tout ca pas de.probleme

bonsoir

ben tu rajoutes la logique nécessaire, en VHDL c'est immédiat si l'on code en VHDL , avec du schéma , maintenant à éviter comme la peste, c'est plus compliqué.

Par contre, par pitié, soigne ton orthographe car c'est très pénible à lire.

JR

l'électronique c'est pas du vaudou!

je veux savoir si c'est des anodes ou cathodes communes

Pour éteindre :

- Si c'est des cathodes communes, il s'arrange pour envoyer des "0" ou passer les sorties en 3 états

- Si c'est des anodes communes, il s'arrange pour envoyer des "1" ou passer les sorties en 3 états

Donc il faut que j utiliseun diviseur de frequence parce que la carte a une horloge de 27 Mhz

j ai essaye de faire ca en vhdl pour avoir plusieurs sortit dont une de 1 hertz

Code:library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_ARITH.all; use IEEE.STD_LOGIC_UNSIGNED.all; ENTITY clk_div IS PORT ( clock_27Mhz : IN STD_LOGIC; clock_1MHz : OUT STD_LOGIC; clock_100KHz : OUT STD_LOGIC; clock_10KHz : OUT STD_LOGIC; clock_1KHz : OUT STD_LOGIC; clock_100Hz : OUT STD_LOGIC; clock_10Hz : OUT STD_LOGIC; clock_1Hz : OUT STD_LOGIC); END clk_div; ARCHITECTURE a OF clk_div IS SIGNAL count_1Mhz: STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL count_100Khz, count_10Khz, count_1Khz : STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL count_100hz, count_10hz, count_1hz : STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL clock_1Mhz_int, clock_100Khz_int, clock_10Khz_int, clock_1Khz_int: STD_LOGIC; SIGNAL clock_100hz_int, clock_10Hz_int, clock_1Hz_int : STD_LOGIC; BEGIN PROCESS BEGIN -- Divise par 27 WAIT UNTIL clock_27Mhz'EVENT and clock_27Mhz = '1' ; IF count_1Mhz < 26 THEN count_1Mhz <= count_1Mhz + 1; ELSE count_1Mhz <= "00000" ; END IF; IF count_1Mhz < 13 THEN clock_1Mhz_int <= '0'; ELSE clock_1Mhz_int <= '1' ; END IF; clock_1Mhz <= clock_1Mhz_int; clock_100Khz <= clock_100Khz_int; clock_10Khz <= clock_10Khz_int; clock_1Khz <= clock_1Khz_int; clock_100hz <= clock_100hz_int; clock_10hz <= clock_10hz_int; clock_1hz <= clock_1hz_int; END PROCESS; -- Divise par 10 PROCESS BEGIN WAIT UNTIL clock_1Mhz_int'EVENT and clock_1Mhz_int = '1'; IF count_100Khz /= 4 THEN count_100Khz <= count_100Khz + 1; ELSE count_100khz <= "000"; clock_100Khz_int <= NOT clock_100Khz_int; END IF; END PROCESS; -- Divise par 10 PROCESS BEGIN WAIT UNTIL clock_100Khz_int'EVENT and clock_100Khz_int = '1'; IF count_10Khz /= 4 THEN count_10Khz <= count_10Khz + 1; ELSE count_10khz <= "000"; clock_10Khz_int <= NOT clock_10Khz_int; END IF; END PROCESS; -- Divise par 10 PROCESS BEGIN WAIT UNTIL clock_10Khz_int'EVENT and clock_10Khz_int = '1'; IF count_1Khz /= 4 THEN count_1Khz <= count_1Khz + 1; ELSE count_1khz <= "000"; clock_1Khz_int <= NOT clock_1Khz_int; END IF; END PROCESS; -- Divise par 10 PROCESS BEGIN WAIT UNTIL clock_1Khz_int'EVENT and clock_1Khz_int = '1'; IF count_100hz /= 4 THEN count_100hz <= count_100hz + 1; ELSE count_100hz <= "000"; clock_100hz_int <= NOT clock_100hz_int; END IF; END PROCESS; -- Divise par 10 PROCESS BEGIN WAIT UNTIL clock_100hz_int'EVENT and clock_100hz_int = '1'; IF count_10hz /= 4 THEN count_10hz <= count_10hz + 1; ELSE count_10hz <= "000"; clock_10hz_int <= NOT clock_10hz_int; END IF; END PROCESS; -- Divise par 10 PROCESS BEGIN WAIT UNTIL clock_10hz_int'EVENT and clock_10hz_int = '1'; IF count_1hz /= 4 THEN count_1hz <= count_1hz + 1; ELSE count_1hz <= "000"; clock_1hz_int <= NOT clock_1hz_int; END IF; END PROCESS; END a;

Dernière modification par Antoane ; 27/11/2017 à 19h44. Motif: Remplacement des balises 'quote' par 'code'

Bonjour,

Ce n'est pas propre car disposer d'un FPGA performant et faire des diviseurs en ripple clock c'est une hérésie et cela bouffe l'arbre d'horloge!

voila un code correct avec l'ajout d'un reset , d'une façon générale et impérative il faut toujours une initialisation , ne pas prendre exemple sur les softeux qui bien souvent n'initialisent pas les variables et pleurent ensuite(du vécu à répétition):

Nota :L'horloge 1 MHZ n'a pas un rapport cyclique de 50%.Code:library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_ARITH.all; use IEEE.STD_LOGIC_UNSIGNED.all; ENTITY clk_div IS PORT ( clock_27Mhz : IN STD_LOGIC; reset : IN STD_LOGIC; clock_1MHz : OUT STD_LOGIC; clock_100KHz : OUT STD_LOGIC; clock_10KHz : OUT STD_LOGIC; clock_1KHz : OUT STD_LOGIC; clock_100Hz : OUT STD_LOGIC; clock_10Hz : OUT STD_LOGIC; clock_1Hz : OUT STD_LOGIC); END clk_div; ARCHITECTURE a OF clk_div IS SIGNAL count_1Mhz: STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL count_100Khz, count_10Khz, count_1Khz,count_100hz, count_10hz, count_1hz : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN PROCESS BEGIN -- Divise par 27 IF reset = '0' THEN count_1Mhz <= (others => '0'); count_100Khz <= (others => '0'); count_10Khz <= (others => '0'); count_1Khz <= (others => '0'); count_100hz <= (others => '0'); count_10hz <= (others => '0'); count_1hz <= (others => '0'); ELSIF rising_edge (clock_27Mhz) THEN ; IF count_1Mhz < 26 THEN count_1Mhz <= count_1Mhz + 1; ELSE count_1Mhz <= (others => '0'); IF count_100khz < 9 THEN count_100khz <= count_100khz + 1; ELSE count_100khz <= (others => '0') ; IF count_10khz < 9 THEN count_10khz <= count_10khz + 1; ELSE count_10khz <= (others => '0') ; IF count_1khz < 9 THEN count_1khz <= count_1khz + 1; ELSE count_1khz <= (others => '0') ; IF count_100hz < 9 THEN count_100hz <= count_100hz + 1; ELSE count_100hz <= (others => '0') ; IF count_10hz < 9 THEN count_10hz <= count_10hz + 1; ELSE count_10hz <= (others => '0') ; IF count_1hz < 9 THEN count_1hz <= count_1hz + 1; ELSE count_1hz <= (others => '0') ; END IF; END IF; END IF; END IF; END IF; END IF; END IF; IF count_1Mhz < 13 THEN clock_1Mhz <= '0'; ELSE clock_1Mhz <= '1' ; END IF; IF count_100khz < 5 THEN clock_100Khz <= '0'; ELSE clock_100Khz <= '1' ; END IF; IF count_10khz < 5 THEN clock_10Khz <= '0'; ELSE clock_10Khz <= '1' ; END IF; IF count_1khz < 5 THEN clock_1Khz <= '0'; ELSE clock_1Khz <= '1' ; END IF; IF count_100hz < 5 THEN clock_100hz <= '0'; ELSE clock_100hz <= '1' ; END IF; IF count_10hz < 5 THEN clock_10hz <= '0'; ELSE clock_10hz <= '1' ; END IF; IF count_1hz < 5 THEN clock_1hz <= '0'; ELSE clock_1Khz <= '1' ; END IF; END PROCESS; END a;

mais pour bien faire il faudrait différentier les signaux d'horloges secondaires pour ne disposer que d'une impulsion de largeur d'un cycle à 27MHz pour pouvoir les utiliser ailleurs en signal de validation tout en conservant une horloge globale à 27 MHz.

JR

l'électronique c'est pas du vaudou!

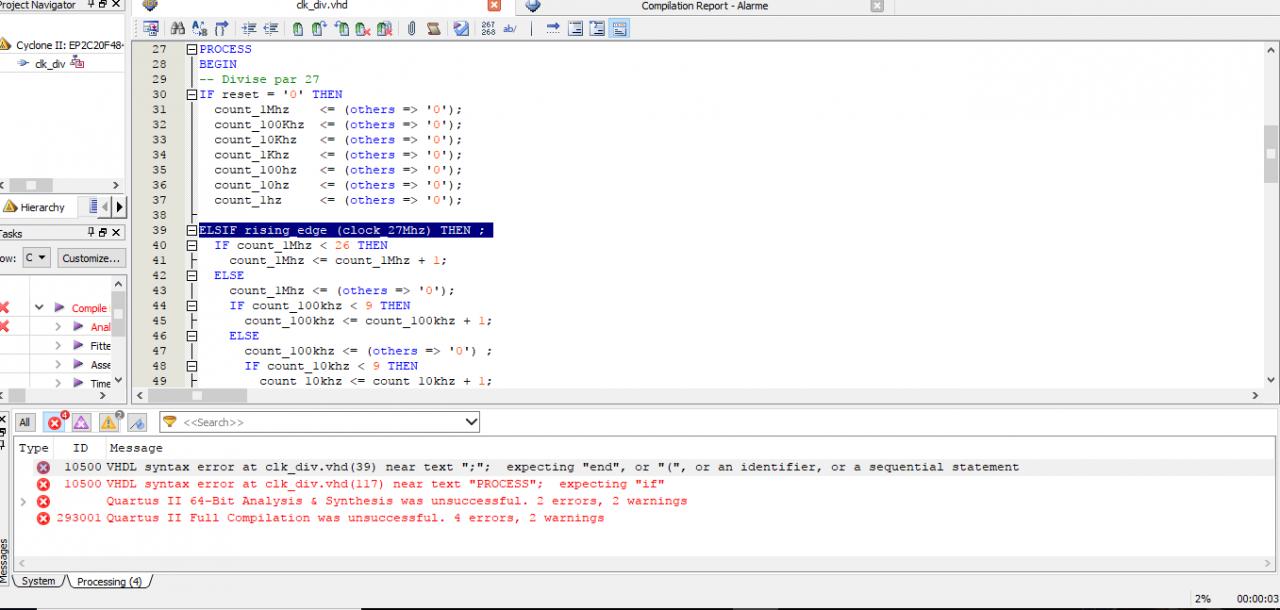

lorsque j essaye de compiler ton code vhdl il m indique des erreursBonjour,

Ce n'est pas propre car disposer d'un FPGA performant et faire des diviseurs en ripple clock c'est une hérésie et cela bouffe l'arbre d'horloge!

voila un code correct avec l'ajout d'un reset , d'une façon générale et impérative il faut toujours une initialisation , ne pas prendre exemple sur les softeux qui bien souvent n'initialisent pas les variables et pleurent ensuite(du vécu à répétition):

Nota :L'horloge 1 MHZ n'a pas un rapport cyclique de 50%.

mais pour bien faire il faudrait différentier les signaux d'horloges secondaires pour ne disposer que d'une impulsion de largeur d'un cycle à 27MHz pour pouvoir les utiliser ailleurs en signal de validation tout en conservant une horloge globale à 27 MHz.

JR

Bonsoir,

Je m'étais pris les pieds dans les indentations et il manquait la liste de sensibilité.

Cela compile avec modelsim et cela devrait fonctionner mais je n'ai pas simulé.Code:library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_ARITH.all; use IEEE.STD_LOGIC_UNSIGNED.all; ENTITY clk_div IS PORT ( clock_27Mhz : IN STD_LOGIC; reset : IN STD_LOGIC; clock_1MHz : OUT STD_LOGIC; clock_100KHz : OUT STD_LOGIC; clock_10KHz : OUT STD_LOGIC; clock_1KHz : OUT STD_LOGIC; clock_100Hz : OUT STD_LOGIC; clock_10Hz : OUT STD_LOGIC; clock_1Hz : OUT STD_LOGIC); END clk_div; ARCHITECTURE a OF clk_div IS SIGNAL count_1Mhz: STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL count_100Khz, count_10Khz, count_1Khz,count_100hz, count_10hz, count_1hz : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN PROCESS(clock_27Mhz,reset) BEGIN -- Divise par 27 IF reset = '0' THEN count_1Mhz <= (others => '0'); count_100Khz <= (others => '0'); count_10Khz <= (others => '0'); count_1Khz <= (others => '0'); count_100hz <= (others => '0'); count_10hz <= (others => '0'); count_1hz <= (others => '0'); ELSIF rising_edge (clock_27Mhz) THEN IF count_1Mhz < 26 THEN count_1Mhz <= count_1Mhz + 1; ELSE count_1Mhz <= (others => '0'); IF count_100khz < 9 THEN count_100khz <= count_100khz + 1; ELSE count_100khz <= (others => '0') ; IF count_10khz < 9 THEN count_10khz <= count_10khz + 1; ELSE count_10khz <= (others => '0') ; IF count_1khz < 9 THEN count_1khz <= count_1khz + 1; ELSE count_1khz <= (others => '0') ; IF count_100hz < 9 THEN count_100hz <= count_100hz + 1; ELSE count_100hz <= (others => '0') ; IF count_10hz < 9 THEN count_10hz <= count_10hz + 1; ELSE count_10hz <= (others => '0') ; IF count_1hz < 9 THEN count_1hz <= count_1hz + 1; ELSE count_1hz <= (others => '0') ; END IF; END IF; END IF; END IF; END IF; END IF; END IF; IF count_1Mhz < 13 THEN clock_1Mhz <= '0'; ELSE clock_1Mhz <= '1' ; END IF; IF count_100khz < 5 THEN clock_100Khz <= '0'; ELSE clock_100Khz <= '1' ; END IF; IF count_10khz < 5 THEN clock_10Khz <= '0'; ELSE clock_10Khz <= '1' ; END IF; IF count_1khz < 5 THEN clock_1Khz <= '0'; ELSE clock_1Khz <= '1' ; END IF; IF count_100hz < 5 THEN clock_100hz <= '0'; ELSE clock_100hz <= '1' ; END IF; IF count_10hz < 5 THEN clock_10hz <= '0'; ELSE clock_10hz <= '1' ; END IF; IF count_1hz < 5 THEN clock_1hz <= '0'; ELSE clock_1Khz <= '1' ; END IF; END IF; END PROCESS; END a;

JR

l'électronique c'est pas du vaudou!

bonsoir,

pour simuler il faut d'abord un simulateur soit le truc natif dans la plupart des outils de développement ou bien Modelsim dont il doit toujours exister une version bridée téléchargeable sur le site Altera.

En suite il faudra encapsuler l'entity dans un autre bloc et générer les stimulus nécessaires à son fonctionnement , ici l'horloge 27MHz et le signal de reset.

Voila un code fonctionnel, accessoirement qu'il y avait une coquille dans le code pour que le projet clk_div fonctionne.

voila la correction :

et le code du test benchCode:IF count_1hz < 5 THEN clock_1hz <= '0'; ELSE clock_1hz <= '1' ; ici il y avait 1khz copier collé mal modifié. END IF;

Il faut donc avoir un projet dans Modelsim qui inclue clk_div et tb_div , on les compile dans la librairie Work et ensuite on simule tb_div apres avoir ouvert une fenêtre Wave et cela donne çà:Code:-- =============== -- librairies -- =============== library ieee,work ; use ieee.Std_logic_1164.all ; use ieee.Numeric_Std.all; use std.textio.all; -- ================ -- Entity interface entity bidon mais obligatoire -- ================ entity tb_div is end tb_div; --========================= -- Architecture description --========================= architecture sim of tb_div is -- Constant for the entity -- ======================= constant porn_delay : time := 1 us ; -- Reset time duration constant clk_half_period : time := 18.52 ns; --27Mhz signal clock_27Mhz,reset,clock_1MHz,clock_100KHz, clock_10KHz,clock_1KHz,clock_100Hz,clock_10Hz,clock_1Hz: std_logic; begin -- ========================== -- Reset and clock generation -- ========================== clock : process begin clock_27Mhz <= '0' ; cycle : loop clock_27Mhz <= '1' ; wait for ( clk_half_period ) ; clock_27Mhz <= '0' ; wait for ( clk_half_period ) ; end loop cycle ; end process clock ; reset <= '0', '1' after porn_delay; -- ========================== -- entity instanciation -- ========================== i_div : entity work.clk_div port map ( clock_27Mhz => clock_27Mhz, reset => reset, clock_1MHz => clock_1MHz, clock_100KHz => clock_100KHz, clock_10KHz => clock_10KHz, clock_1KHz => clock_1KHz, clock_100Hz => clock_100Hz, clock_10Hz => clock_10Hz, clock_1Hz => clock_1Hz ); end;

Je ne pourrais pas expliquer plus avant le fonctionnement de Modelsim car c'est trop compliqué pour un forum.

JR

l'électronique c'est pas du vaudou!