Bonjour,

J'ai eu une idée qui permettrait d'améliorer la stabilité d'un synthétiseur basé sur un comparateur de fréquences tristate à mémoires comme le CD4046.

J'aimerais avoir votre avis si ça pourrait fonctionner

L'idée est de baisser la pente du VCO, tout en couvrant la même gamme de fréquences.

Le VCO aurait deux commandes à varicaps :

- L'une serait commandée par une tension très stable dépendant du taux de division pour amener le VCO dans la bonne plage

- L'autre serait contrôlée par le filtre de la PLL comme d'habitude

Le tout serait sous 8 V

Pas de synthèse : 1 KHz

La plage à couvrir est de 5 à 6 MHz

Le diviseur programmable est déjà créé et a un taux de division de 5000 à 5999

Pour les varicaps connectées au filtre de la PLL, il faudrait les commander avec une tension pas trop basse, et les charges / décharges des capas du filtre doivent rester à peu près linéaires, donc proches de Vdd/2. Pour la plage de fréquences voulue, il faudrait donc 2,5 V pour avoir 5 MHz, et 5,5 V pour avoir 6 MHz (de Vdd/2 - 1,5 V à Vdd/2 + 1,5 V)

Première commande par varicaps : Tension très stable crée à partir du chiffre des centaines du diviseur

Le VCO accélère quand le taux de division augmente, donc, on peut prélever le chiffre des centaines, le convertir en tension, l'appliquer aux varicaps, et amener le VCO proche de la fréquence voulue

2,5 à 6,55 V = 4,05 V pour une plage de 900 KHz : 100 KHz/0,45 V, soit environ 222 KHz/V, voir tableau en dessous

J'ai ma petite idée pour produire ces tension espacées de 0,45 V à partir de la valeur binaire du compteurCode:Chiffre des centaines du diviseur Tension de commande à appliquer (V) Fréquence approchée voulue (MHz) (5000 à 5999) (0,45 V par centaine, offset 2,5 V) 0 2,50 5,0 1 2,95 5,1 2 3,40 5,2 3 3,85 5,3 4 4,30 5,4 5 4,75 5,5 6 5,20 5,6 7 5,65 5,7 8 6,10 5,8 9 6,55 5,9

Elles seront crées en partie avec un AOP faible bruit, c'est pour ça que je laisse une marge entre 6,55 V et Vdd (8 V)

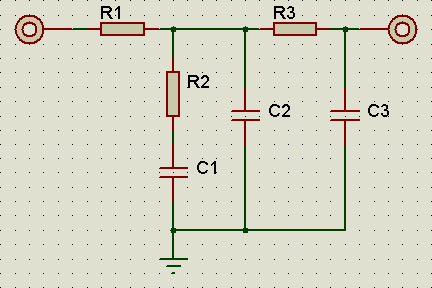

Deuxième commande par varicaps : Tension venant du filtre de la PLL

On voit dans le tableau au dessus qu'on a une erreur au maximum de 100 KHz que la PLL devra rattraper avec une tension allant de 2,5 V à 5,5 V venant du filtre, ce qui fait une pente d'environ 33 KHz/V

Un exemple :

On choisit un taux de division de 5729 qui fera 5,729 MHz (1 KHz * 5729 = 5,729 MHz)

Le chiffre des centaines vaut 7

Donc sur la première commande de varicaps, 5,65 V sont appliqués, ce qui amène le VCO à 5,7 MHz, proche de la fréquence voulue (voir tableau)

La deuxième commande à varicaps est contrôlée par la PLL et va amener le VCO exactement à la bonne fréquence

Sans la première source de commande du VCO, on aurait eu besoin de 3 V pour couvrir 1 MHz (333 KHz/V). Maintenant, on a 33 KHz/V. On a donc une pente 10 fois plus faible, et même si le CD4046 reste presque tout le temps en tristate, les résidus auront encore moins d'influence sur le VCO

Le réglage du VCO risque d'être assez musclé, je sais que je ne pourrais jamais réaliser tout ça avec les chiffres exacts du tableau, donc, des marges de sécurité sont à prévoir pour être sûr de pouvoir couvrir toutes les fréquences

Il va falloir plus de varicaps qu'un montage plus courant, donc du bruit en plus. Et la partie qui va convertir la valeur binaire du compteur en tensions, va elle aussi apporter du bruit.

Bien sûr, circuit impeccable, régulateur faible bruit LM723

D'un coté, on a le choix d'un circuit plus standard pas trop bruyant, mais un VCO avec une pente élevée

De l'autre, on a plus de bruit mais un VCO avec une pente bien plus faible

Voilà pourquoi je me demande si ça peut apporter cette amélioration ou pas

Merci

-----