Bonjour,

actuellement, je suis sur un problème au niveau de mon code VHDL.

Je dois réaliser un fréquencemètre à partir de ma fréquence du FPGA qui est de 100Mhz.

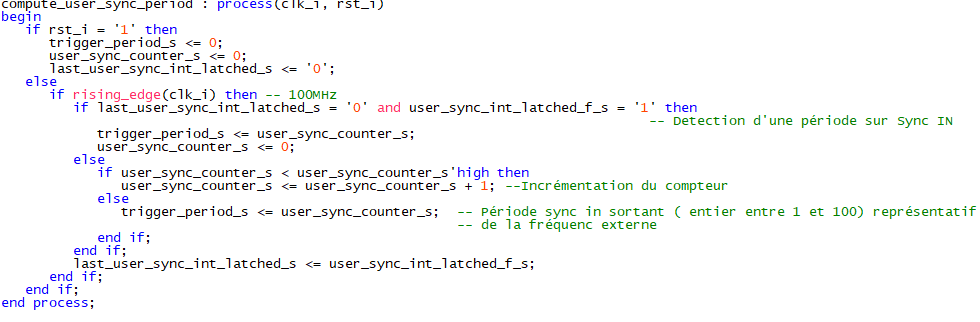

Voici le code :

Imaginons que je met une fréquence externe de 20Mhz, l'entier sortant de cette fonction doit être 5 mais dans mon cas, l'entier varie entre 5 et 6 donc entre 16.6 et 20MHz.

Il est ici mon problème... Quelqu'un aurait une idée ?

Merci d'avance.

Axel G

-----