Bonjour,

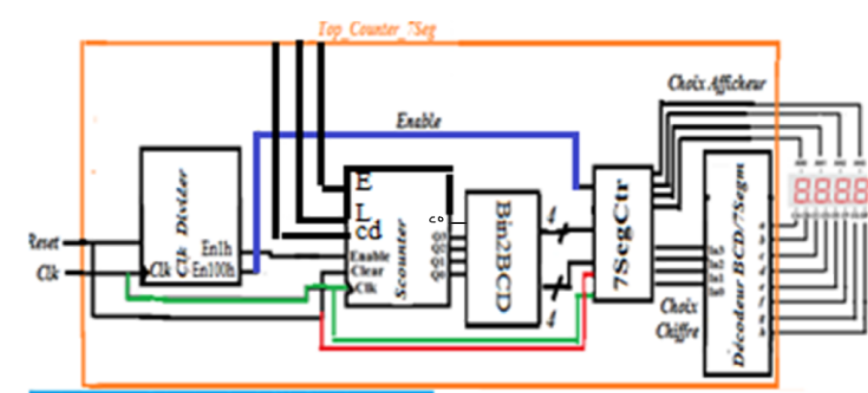

J'essaie d'implémenter un compteur modulo 100.

Je rencontre quelques problèmes avec la partie Bin2BCD.

Le fait est que l'incrémentation du chiffre des dizaines se fait deux par deux, ça passe de 0 à 2 puis à 4 etc... et je ne comprends pas

pourquoi ?

La structure du compteur mod100: schema.png

Code de la partie Bin2BCD: bin2bcd.txt

Merci pour toutes éventuelles aides

P.S: Voici également le code des autres blocs Codes.rar .

P.S2: J'exécute la simulation sur ISE et cela prend trop de temps. Un truc à me proposer pour réduire le temps de simulation ? (réduire la résolution temporelle ou un truc du genre)

-----