Bonjour à tous,

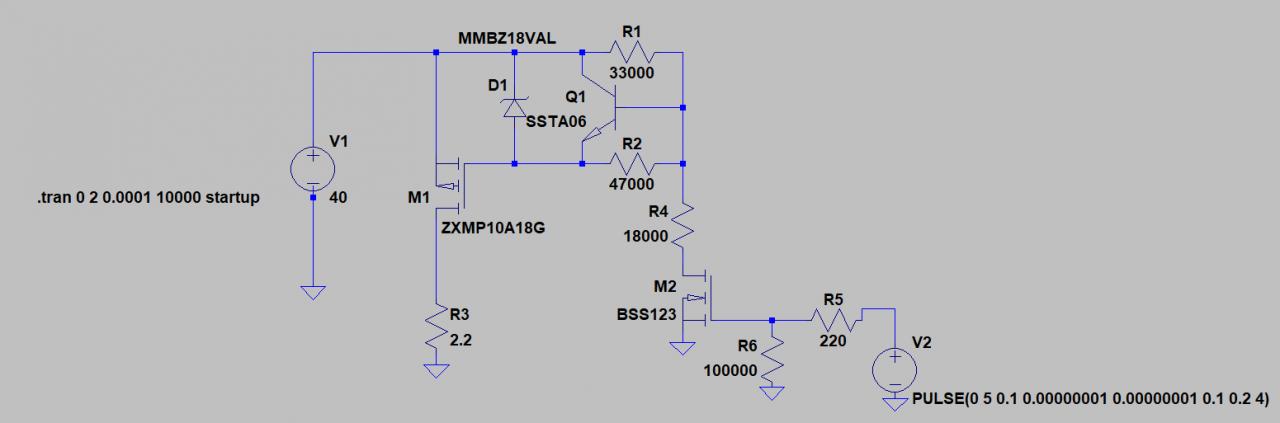

Je travaille depuis un petit moments avec ce montage suivant :

Dans la vie réel, ce montage fonctionne bien mais de temps en temps et ça je ne l'avais pas prévue, des surtensions apparaissent aux niveau de mon alimentation. Le gros PMOS survie aux surtensions mais il arrive des fois que ce soit Q1 qui décède.

J'ai réaliser des calculs et des simulations. j'en suis venu a la conclusion suivante que Q1 meurt car la tension VEB dépasse les 6V.

Lorsque M2 est saturé (ce qui est quasiment toujours le cas) :

Si VCC = 40V, je me retrouve avec VR2 = VEB = VCC - VR4 - VDZ1.

VDZ1 est un zener de 18V, VR4 = 40(R4 / (R1+R4)) = 14.12V environs.

Donc mon VEB = 40 - 18 - 14.12 = 7.88V > 6V.

Sachant que mon VCC peut hypothétiquement (et cela doit arriver) dépasser 40V, voici mes question :

1) Est que c'est possible que Q1 finisse avec sa jonction en CC entre sa base et son émetteur si VEBO est dépassé ?

2) Quand je fait des essais sur plaque lab ... et ben je remarque que VEB dépasse VEBO mais le transistor marche toujours bien après ... je n'arrive pas a le mourrut ! (donc je suis pas sur de mon hypothèse).

3) SI c'est la cause, comment je peut protéger mon VEB sachant que je ne connais pas les valeurs maximales de tension pouvant apparaitre sur VCC (autre qu'une TVS sur la ligne VCC).

Merci d'avance pour vos lumières

-----