Bonjour,

Je cherche à utiliser un ADC (en fait un modulateur sigma-delta isolé) ACPL-C740 (https://docs.broadcom.com/doc/ACPL-C740-DS) pour mesurer de manière isolée la tension d'un bus DC V_HV.

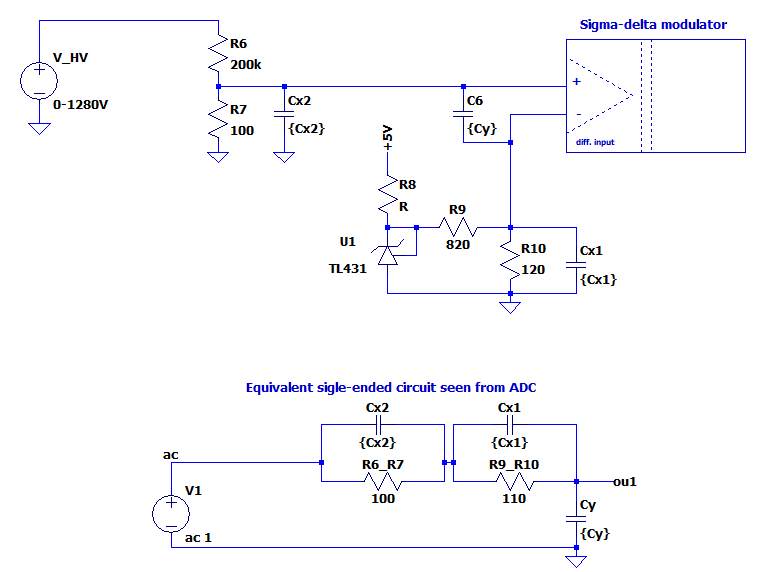

L'ADC a une entrée différentielle, et une plage de tension d'entrée acceptable de +/-320 mV (+/-200 mV pour la pleine performance). Comme mon bus DC est unipolaire, je connecte l'entrée "-" de l'ADC à un potentiel de 320 mV, et l'entrée "+" au BUS DC, via un pont diviseur.

Voici le schéma du circuit utilisé, ainsi que le circuit equivalent en single-ended vu depuis l'ADC :

Ma question porte sur le dimensionnement du filtre d'entrée :

- le pont diviseur R6-R7 pour mesurer la tension V_HV (0 - 1280 V, ou 240V - 1040V pour la pleine performance) n'est pas vraiment un degré de liberté : il est contraint en particulier par la puissance maximale pouvant y être dissipée et par la resistance max assurant une bonne dynamique. Par ailleurs, sa résistance équivalente vue depuis l'ADC est, avec les valeurs indiquées sur le schéma, faible (~100Ohm).

- Le pont diviseur R9-R10 créant la référence de 320mV à partir du 2.495V délivré par le TL431 est relativement peu contraint, mais difficile de descendre en deca de ~100Ohm pour R10. Avec les valeurs choisies, la résistance équivalente vue depuis l'ADC est ~100Ohm, ce qui est faible et similaire à ce qui est vu par l'autre entrée de l'ADC.

- La question principale porte alors sur Cx1, Cx2, et Cy : comment les dimensionner ?

- Avec une entrée différentielle et un signal d'entrée différentiel, je serais dans une situation typique et prendrais les valeur recommandées par la datasheet : Cx~0, Cy~22nF.

- Cependant, mon entrée n'est pas vraiment un signal différentiel mais deux signaux single-ended (le bruit sur chacune des entrées est référencé à la masse, il n'y a pas de corrélation entre les bruits venant des signaux d'entrée). Ce n'est pas non plus le cas d'un signal signle-ended qu'il faudrait symétriser. Du coup, j'aurais envie de dimensionner chaque Cx en fonction du bruit/spectre du signal single-ended qu'il filtre -- mais on se retrouve alors potenstiellement avec des valeurs de Cx1 et Cx2 différentes, et Cy reste à choisir... je ne vois pas comment faire un design optimal.

La bande passante requise, peu critique, est de l'ordre de 600 Hz.

Question annexe : j'avais initialement pris des valeurs de R9 et R10 10 fois plus élevées (le pb était que le courant de fuite de l'ADC causait alors un offset trop grand), ajoutant une assymétrie au design... Que je savais alors encore moins de symmétrie entre les impédances vues par les entrées, et la résolution était moins évidente.

Le choix du ACPL-C740 n'était peut-être (sans doute) pas optimal, mais en changer n'est plus une option, le PCB comme la commande digikey sont dans le labo

Merci de m'avoir lu, et merci d'avance pour vos idées !

-----