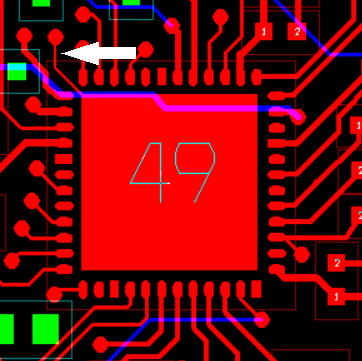

D'autant plus, que d'après la doc, ils placeraient des vias sur une partie du composant

Plan constructeur.png

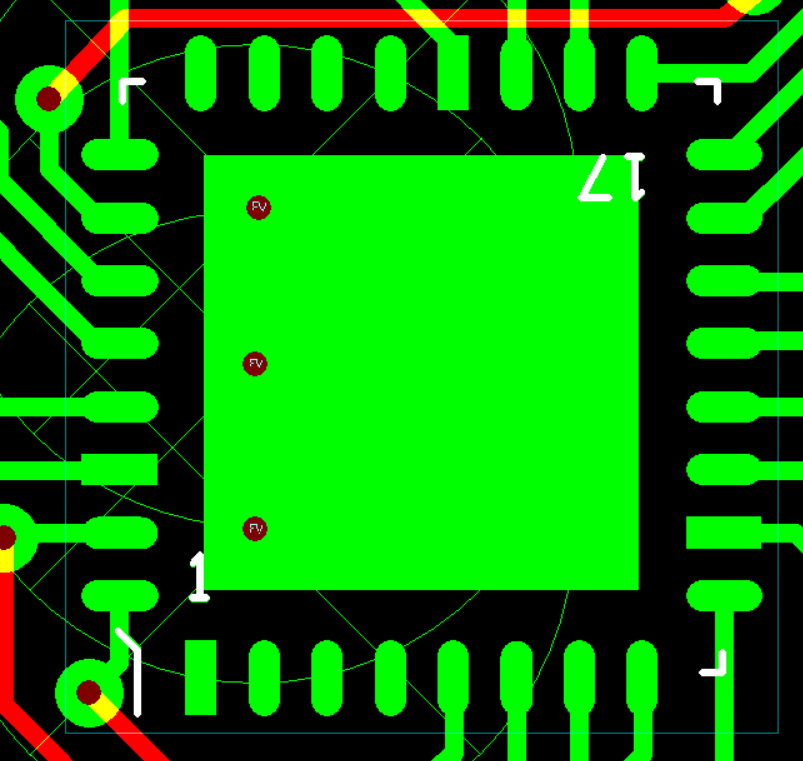

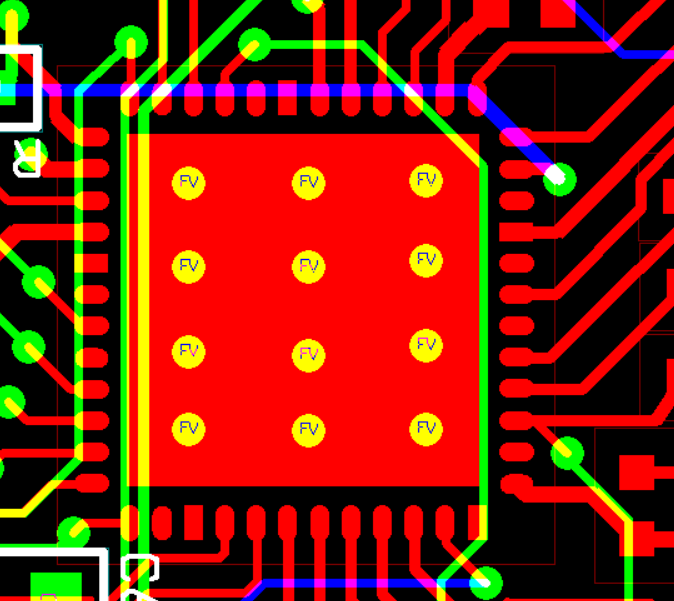

Alors que le plan de l'empreinte place les 5 vias à une autre position sauf erreur ?...

footprint.png

pour que ceuc-ci soit en AGND, il serait logique de les mettre que d'un côté...

Merci

-----