Bonjour à tous,

Sur ce shéma, http://searle.x10host.com/6809/Simple6809.html

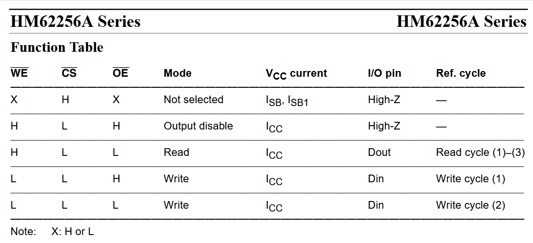

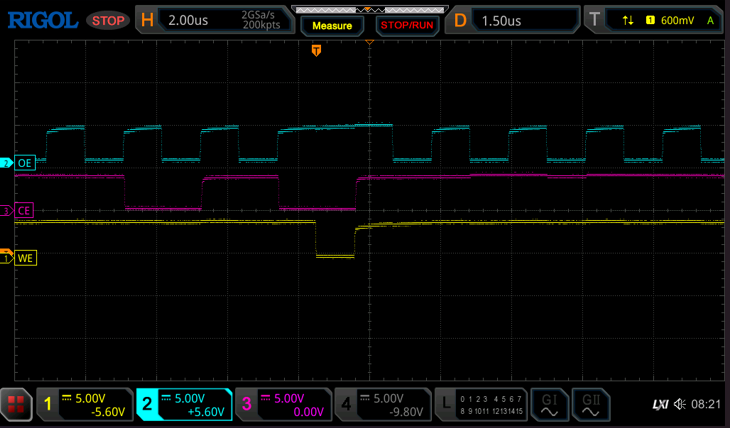

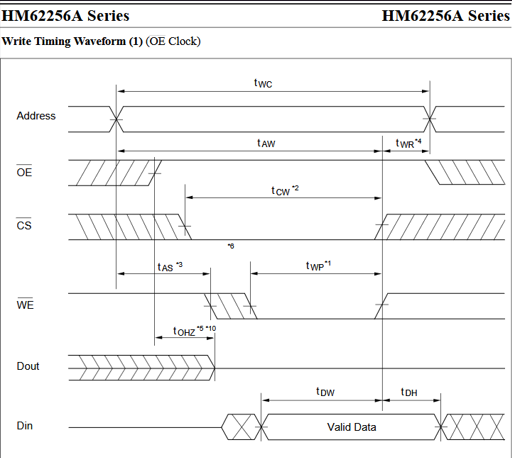

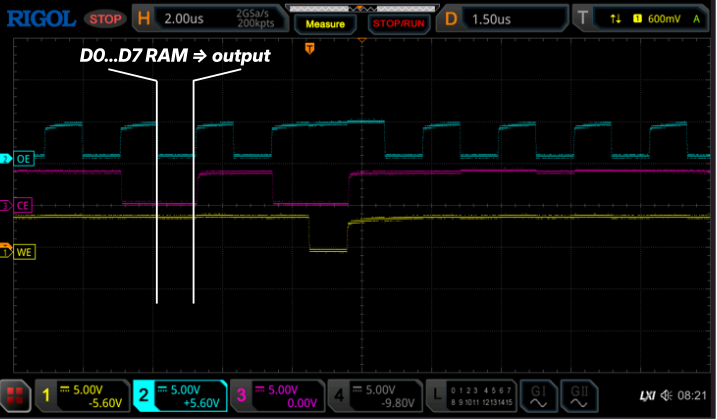

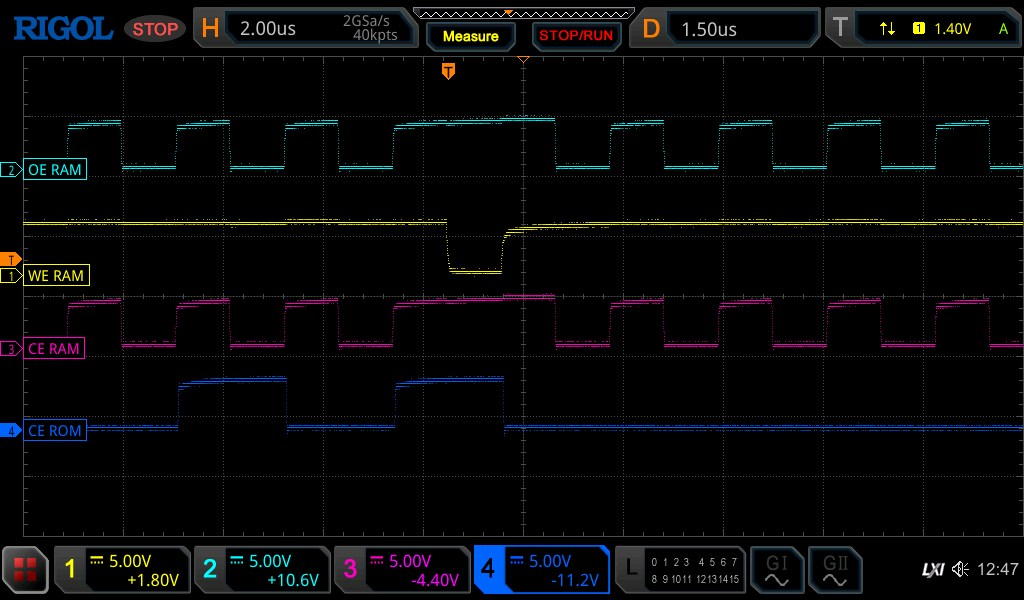

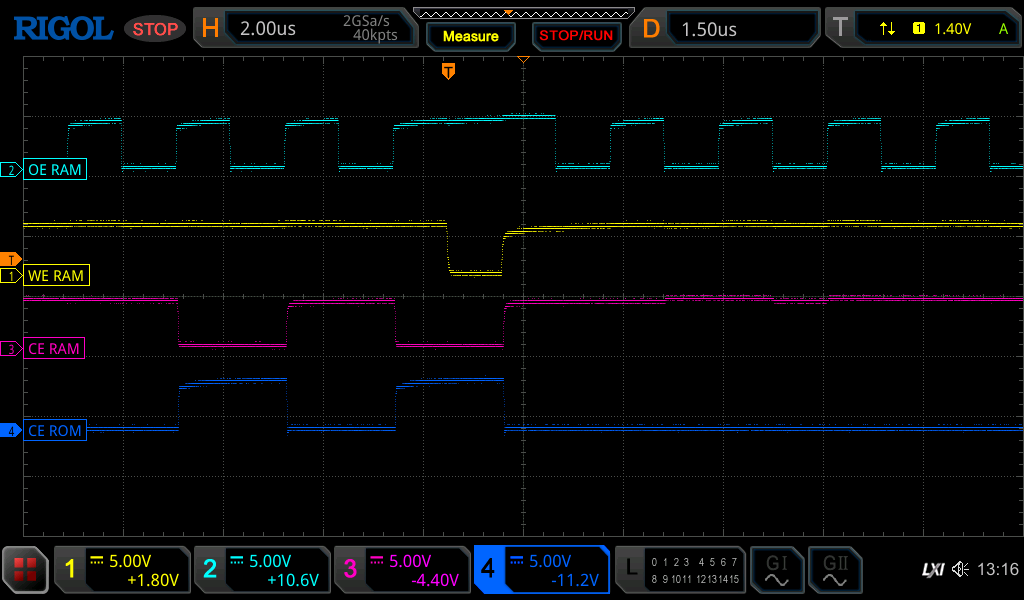

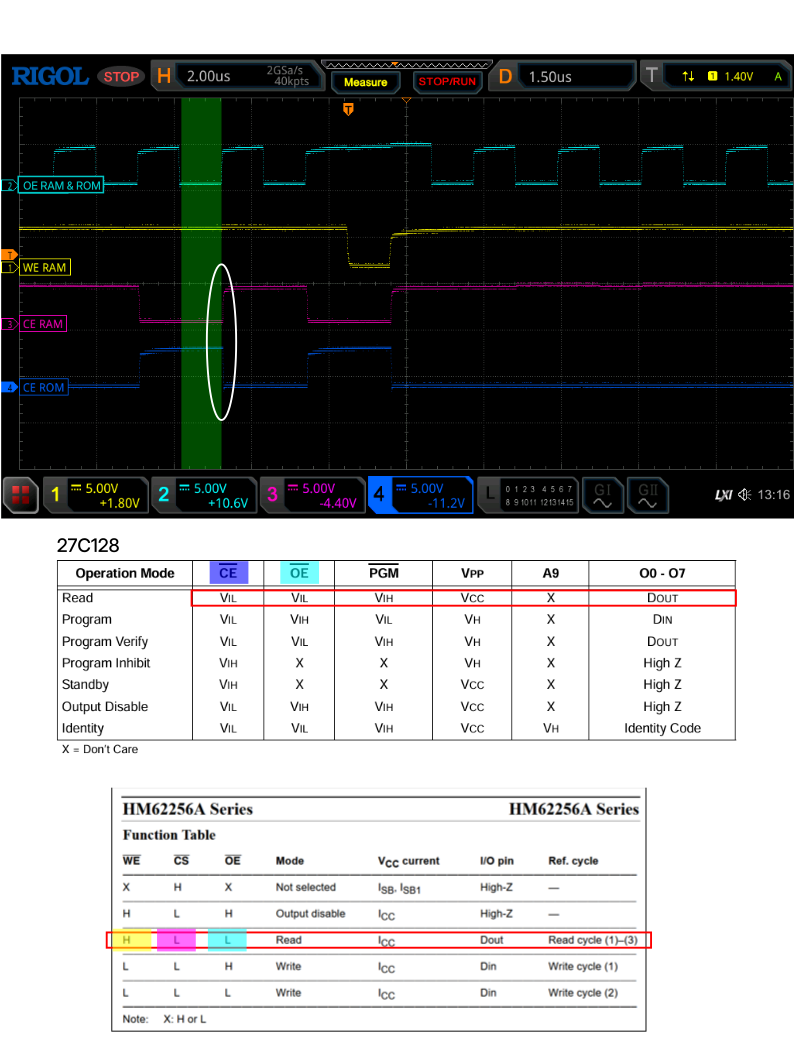

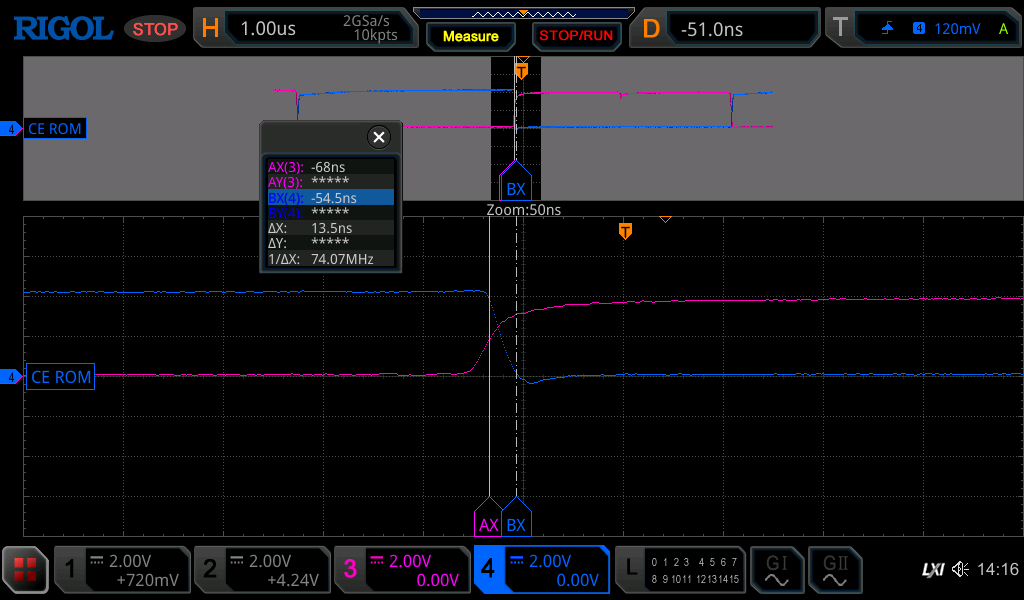

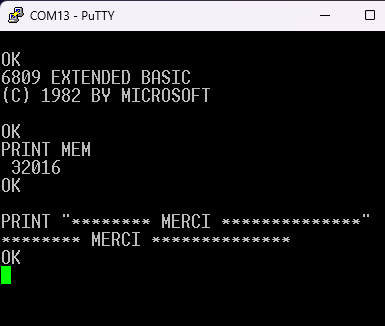

il faut que j' enlève la liaison entre la pin OE/ de la RAM et la porte U6B et que je mette OE/ RAM au GND pour que le programme

fonctionne

Qu'est ce qui peut empecher le montage de fonctionner comme il cablé sur le schema

José

-----