Bonjour à tous,

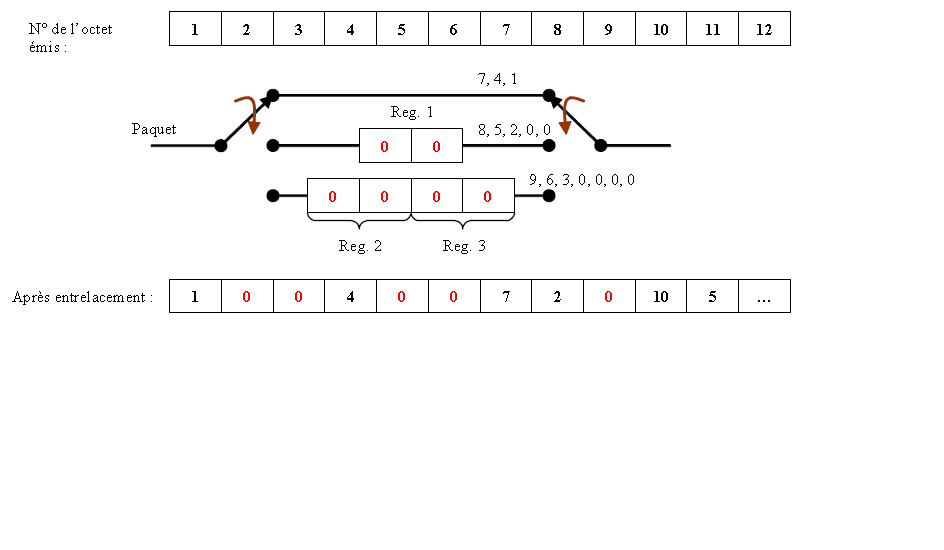

Voici l'entrelaceur que je cherche à implémenter en VHDL, c'est un entrelaceur convolutionnel fonctionne comme suit

Il y a trois branches: sur les 2 dernieres il y a plusieurs "memoires"..

En entrée on vient successivement écrire sur chaque ligne un nombre (à chaque coup de clock)

De même en sortie, on lit succesivement chaque ligne...

Au depart les mémoires sont vides..

A ck1 (coup de clock 1) on ecrit le premier nombre sur la premiere ligne qu'on lit en même temps -> sortie =1

A ck2 on ecrit 2 sur la première mémoire de la ligne 2 et on lit la dernières mémoires (qui est vide) => 0 (On decale ensuite(ou juste avant le prochain passage) chaque mémoire, le "2" bouge")

A ck3 idem mais sur troiseme ligne (3 est dans la première "mémoire" et 0 dans dernière) => sortie =0

A ck4 on revient à la première ligne, ou on récrit la sortie= entrée=> sortie=4

Et ainsi de suite...a chaque passage de ligne on decale les mémoires, il faut donc plusieurs tours avant que la première valeur ecrite dans les mémoires d'un ligne sorte...

SVP quel qu'un peut m'aider de faire le code avec VHDL

merciii

-----