Bonjour,

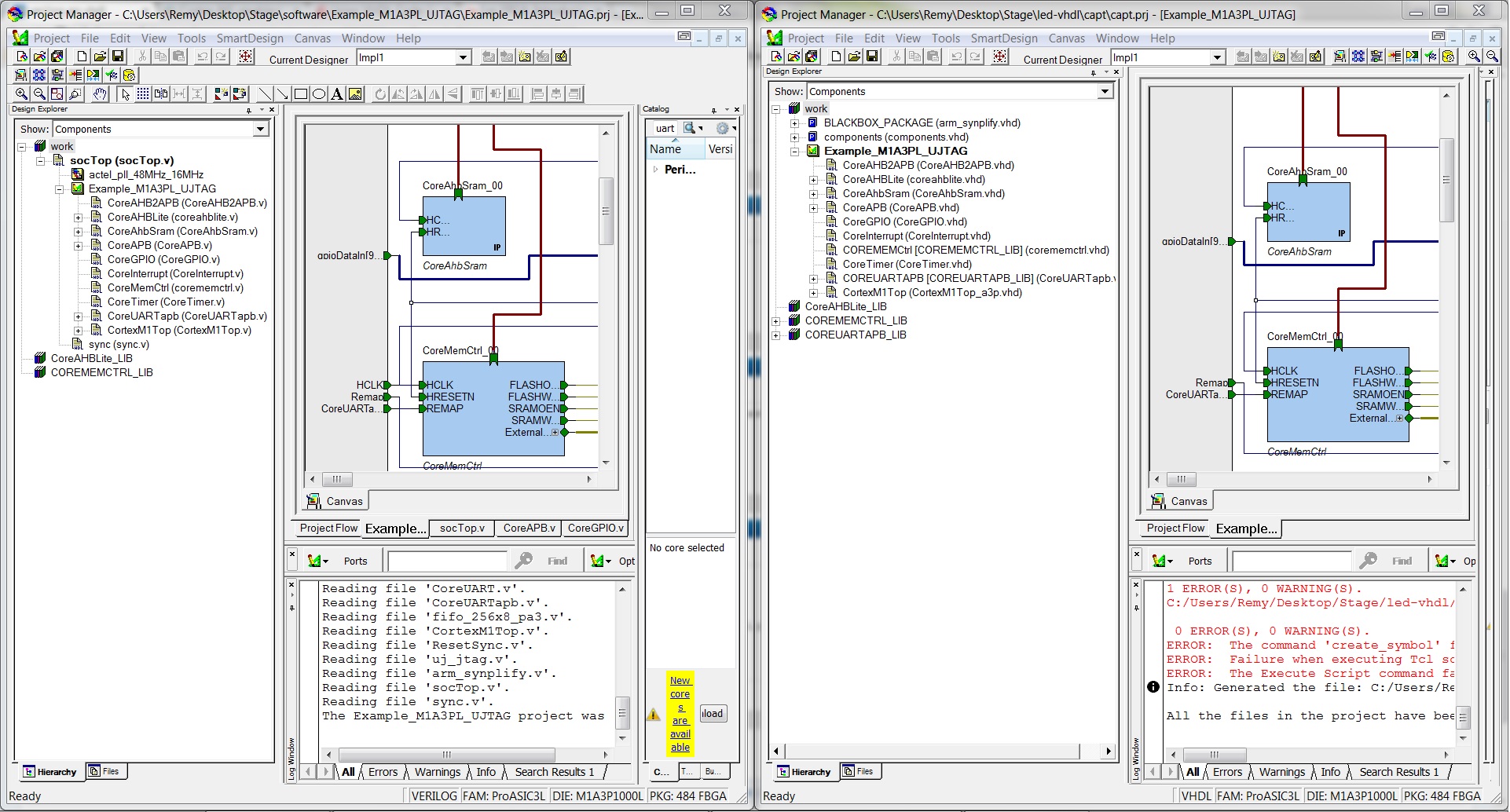

Mon objectif est de programmer un capteur d'image en vhdl. Pour cela je suis parti d'un fichier exemple.. mais il est en verilog.

Voila se que donne ma conversion (elle ne marche pas)Code:`define N_EXT_ADDR 26 module socTop ( pbRstN, poRstN, flashRstN, sysClk, rs232Atx, rs232Arx, extAddr, extData, flashHiCeN, flashLoCeN, flashWeN, flashOeN, sramCeN, sramBsN, sramWeN, sramOeN, ledOut, switchIn, UJTAG_UJTAG_TCK, UJTAG_UJTAG_TDI, UJTAG_UJTAG_TMS, UJTAG_UJTAG_TRSTB, UJTAG_UJTAG_TDO, /* JTCK, JTDI, JTMS, JRTCK, JTDO, */ sysClk_16MHz, pllLock, dummyIn, dummyOut ); /* synthesis syn_global_buffers = 10 */ // I/O definitions: // System clocks: input sysClk; // Resets: input pbRstN; // external reset connected to pushbutton input poRstN; // external reset not connected to pushbutton output flashRstN; // reset to FLASH // RS232 connections: output rs232Atx; // serial transmit line input rs232Arx; // serial receive line // External FLASH/RAM signals: inout [31:0] extData; // bidirectional data to external devices output [`N_EXT_ADDR-1:2] extAddr; output flashHiCeN; output flashLoCeN; output flashWeN; output flashOeN; output sramCeN; output [3:0] sramBsN; // SRAM Byte Select signals output sramWeN; output sramOeN; // Switches, LEDs output [9:0] ledOut; input [9:0] switchIn; // JTAG for FlashPro3 connector input UJTAG_UJTAG_TCK; input UJTAG_UJTAG_TDI; input UJTAG_UJTAG_TMS; input UJTAG_UJTAG_TRSTB; output UJTAG_UJTAG_TDO; /* // ICE Debug connector input JTCK; input JTDI; input JTMS; output JRTCK; output JTDO; */ // Pll signals output sysClk_16MHz; output pllLock; // Dummy signals input dummyIn; output dummyOut; // Declarations: // Clocks, Resets wire sysClk_48MHz; wire sysClk_16MHz; wire poRstNi; wire pbRstNi; // APB slave interface wire HRESETN; wire [31:0] APBmslave0_PRDATA; wire [23:0] APBmslave0_PADDR; wire APBmslave0_PENABLE; wire APBmslave0_PSELx; wire [31:0] APBmslave0_PWDATA; wire APBmslave0_PWRITE; // GPIO signals wire [9:0] gpioDataIn; wire [9:0] gpioDataOut; // ARM debugger wire nTDOEN; wire JTDOi; // External memories wire [27:0] memAddr; wire flashCeN; wire flashOeN; wire sramOeN; // Remap wire Remap; // Switch wire [9:0] switchInSync; // Assignments: // Keep these from being unused inputs assign dummyOut = dummyIn; // Connect LEDs & switches to GPIO assign ledOut = gpioDataOut; assign gpioDataIn = switchInSync; /* // ICE debugger assign JTDO = nTDOEN ? 1'bZ : JTDOi; */ // External memories assign flashRstN = pbRstNi; assign flashHiCeN = flashCeN; assign flashLoCeN = flashCeN; assign extAddr[`N_EXT_ADDR-1:2] = memAddr[`N_EXT_ADDR-3:0]; //assign memOeN = flashOeN & sramOeN; // Remap assign Remap = ~switchInSync[9]; //Note that switchIn[9] governs remapping // Instantiations: // Global resources for clock, reset actel_pll_48MHz_16MHz pll1 (.POWERDOWN(poRstNi), .CLKA(sysClk_48MHz), .LOCK(pllLock), .GLA(sysClk_16MHz)); CLKINT ci0 (.A(sysClk), .Y(sysClk_48MHz)); CLKINT ci1 (.A(poRstN), .Y(poRstNi)); CLKINT ci2 (.A(pbRstN), .Y(pbRstNi)); // Instantiate Cortex-M1 Subsystem: Example_M1A3PL_UJTAG Example_M1A3PL_UJTAG_00( // Inputs .CoreUARTapbRX (rs232Arx), .gpioDataIn (gpioDataIn), .HCLK (sysClk_16MHz), .NSYSRESET (pbRstNi), .UJTAG_UJTAG_TCK (UJTAG_UJTAG_TCK), .UJTAG_UJTAG_TDI (UJTAG_UJTAG_TDI), .UJTAG_UJTAG_TMS (UJTAG_UJTAG_TMS), .UJTAG_UJTAG_TRSTB (UJTAG_UJTAG_TRSTB), .Remap(Remap), // Outputs .CoreUARTapbTX (rs232Atx), .gpioDataOut (gpioDataOut), .ExternalMemoryInterface_FlashCSN (flashCeN), .ExternalMemoryInterface_FlashOEnN (flashOeN), .ExternalMemoryInterface_FlashWEnN (flashWeN), .ExternalMemoryInterface_MemAddr (memAddr), .ExternalMemoryInterface_MemReadN (), .ExternalMemoryInterface_MemWriteN (), .ExternalMemoryInterface_SramByteN (sramBsN), .ExternalMemoryInterface_SramCSN (sramCeN), .ExternalMemoryInterface_SramClk (), .ExternalMemoryInterface_SramOEnN (sramOeN), .ExternalMemoryInterface_SramWEnN (sramWeN), .HRESETn (HRESETN), .UJTAG_UJTAG_TDO (UJTAG_UJTAG_TDO), // Inouts .ExternalMemoryInterface_MemData (extData) ); sync #(10) sync0 ( .outClk (sysClk_16MHz), .outRstN (HRESETN), .asyncInput (switchIn), .syncOutput (switchInSync) ); endmodule

Un peu long mais je compte sur vous ^^'Code:library IEEE; use IEEE.BIT_1164.all; use IEEE.BIT_arith.all; use IEEE.BIT_unsigned.all; ENTITY mt9v034 is PORT ( sysClk :IN BIT; pbRstN :IN BIT; -- external reset connected to pushbutton poRstN :IN BIT; -- external reset not connected to pushbutton rs232Arx :IN BIT; -- serial receive line LVDS :IN BIT; UJTAG_UJTAG_TCK :IN BIT; -- JTAG for FlashPro3 connector UJTAG_UJTAG_TDI :IN BIT; UJTAG_UJTAG_TMS :IN BIT; UJTAG_UJTAG_TRSTB :IN BIT; dummyIN :IN BIT; -- Dummy signals switchIN :IN BIT; flashRstN :OUT BIT; rs232Atx :OUT BIT; -- serial transmit line flashHiCeN :OUT BIT; flashLoCen :OUT BIT; flashWeN :OUT BIT; flashOeN :OUT BIT; sramCeN :OUT BIT; sramBsn :OUT BIT; -- SRAM Byte Select signals sramWeN :OUT BIT; sramOeN :OUT BIT; dataOut :OUT BIT_vector(9 downto 0); UJTAG_UJTAG_TDO :OUT BIT; sysClk_26_6MHZ :OUT BIT; -- Pll signals pllLock :OUT BIT; -- Pll signals dummyOut :OUT BIT; -- Dummy signals extData : INOUT BIT_VECTOR(31 downto 0); -- bidirectional data to external devices extAddr : OUT BIT_VECTOR(25 downto 2) ); END mt9v034; ARCHITECTURE proasic3l OF mt9v034 IS -- Clocks, Resets signal sysClk_48MHz : BIT; signal sysClk_16MHz : BIT; signal poRstNi : BIT; signal pbRstNi : BIT; -- APB slave interface signal HRESETN : BIT; signal APBmslave0_PENABLE : BIT; signal APBmslave0_PSELx : BIT; signal APBmslave0_PWRITE : BIT; -- ARM debugger signal nTDOEN : BIT; signal JTDOi : BIT; signal flash_CeN : BIT; signal flash_OeN : BIT; signal sram_OeN : BIT; signal Remap : BIT; -- APB slave interface signal APBmslave0_PRDATA : BIT_vector(31 downto 0); signal APBmslave0_PADDR : BIT_vector(23 downto 0); signal APBmslave0_PWDATA : BIT_vector(31 downto 0); -- GPIO signals signal gpioDataIn : BIT; signal gpioDataOut : BIT_vector(9 downto 0); -- External memories signal memAddr : BIT_vector(27 downto 0); signal switchInSync : BIT; component actel_pll_48MHz_16MHz port( POWERDOWN : IN BIT; CLKA : IN BIT; LOCK : OUT BIT; GLA : OUT BIT ); end component; component CLKINT port( A : IN BIT; Y : OUT BIT ); end component; component sync0 port ( asyncInput : IN BIT; outClk : OUT BIT; outRstN : OUT BIT; syncOutput : OUT BIT ); end component; component mt9v034 port ( component inst_mt9v034 port ( CoreUARTapbRX : IN BIT; RESET : IN BIT; HCLK : IN BIT; NSYSRESET : IN BIT; UJTAG_UJTAG_TCK : IN BIT; UJTAG_UJTAG_TDI : IN BIT; UJTAG_UJTAG_TMS : IN BIT; UJTAG_UJTAG_TRSTB : IN BIT; CoreUARTapbTX : OUT BIT; gpioDataOut : OUT BIT_vector(9 downto 0); ExternalMemoryInterface_FlashCSN : OUT BIT; ExternalMemoryInterface_FlashOEnN : OUT BIT; ExternalMemoryInterface_FlashWEnN : OUT BIT; ExternalMemoryInterface_MemAddr : OUT BIT_vector(27 downto 0); ExternalMemoryInterface_SramByteN : OUT BIT; ExternalMemoryInterface_SramCSN : OUT BIT; ExternalMemoryInterface_SramOEnN : OUT BIT; ExternalMemoryInterface_SramWEnN : OUT BIT; HRESETn : OUT BIT; UJTAG_UJTAG_TDO : OUT BIT; ExternalMemoryInterface_MemData : INOUT BIT_VECTOR(31 downto 0) ); end component; ); end component; BEGIN dummyOut <= dummyIn; -- Keep these from being unused inputs dataOut <= gpioDataOut; gpioDataIn <= switchInSync; --External memories flashRstN <= pbRstNi; flashHiCeN <= flash_CeN; flashLoCeN <= flash_CeN; extAddr(25 downto 2) <= memAddr(23 downto 0); Remap <= not(switchInSync); --Instanciations: -- Global resources for clock, reset pll1 : actel_pll_48MHz_16MHz port map ( POWERDOWN => poRstNi, CLKA => sysClk_48MHz, LOCK => pllLock, GLA => sysClk_16MHz ); ci0 : CLKINT port map ( A => sysClk, Y => sysClk_48MHz ); ci1 : CLKINT port map ( A => poRstN, Y => poRstNi ); ci2 : CLKINT port map ( A => poRstN, Y => pbRstNi ); --Instantiate Cortex-M1 Subsystem: mt9v034 : inst_mt9v034 port map ( --Inputs CoreUARTapbRX => rs232Arx, RESET => gpioDataIn, HCLK => sysClk_16MHz, NSYSRESET => pbRstNi, UJTAG_UJTAG_TCK => UJTAG_UJTAG_TCK, UJTAG_UJTAG_TDI => UJTAG_UJTAG_TDI, UJTAG_UJTAG_TMS => UJTAG_UJTAG_TMS, UJTAG_UJTAG_TRSTB => UJTAG_UJTAG_TRSTB, --Outputs CoreUARTapbTX => rs232Atx, gpioDataOut => gpioDataOut, ExternalMemoryInterface_FlashCSN => flashCeN, ExternalMemoryInterface_FlashOEnN => flashOeN, ExternalMemoryInterface_FlashWEnN => flashWeN, ExternalMemoryInterface_MemAddr => memAddr, --ExternalMemoryInterface_MemReadN => , --ExternalMemoryInterface_MemWriteN =>, ExternalMemoryInterface_SramByteN => sramBsN, ExternalMemoryInterface_SramCSN => sramCeN, --ExternalMemoryInterface_SramClk =>, ExternalMemoryInterface_SramOEnN => sramOeN, ExternalMemoryInterface_SramWEnN => sramWeN, HRESETn => HRESETN, UJTAG_UJTAG_TDO => UJTAG_UJTAG_TDO, --Inouts ExternalMemoryInterface_MemData =>extData ); sync : sync0 port map ( outClk => sysClk_16MHz, outRstN => HRESETN, asyncInput => switchIn, syncOutput => switchInSync ); END proasic3l;

Merci

Bartacus

-----