salut les chers membres du groupe;

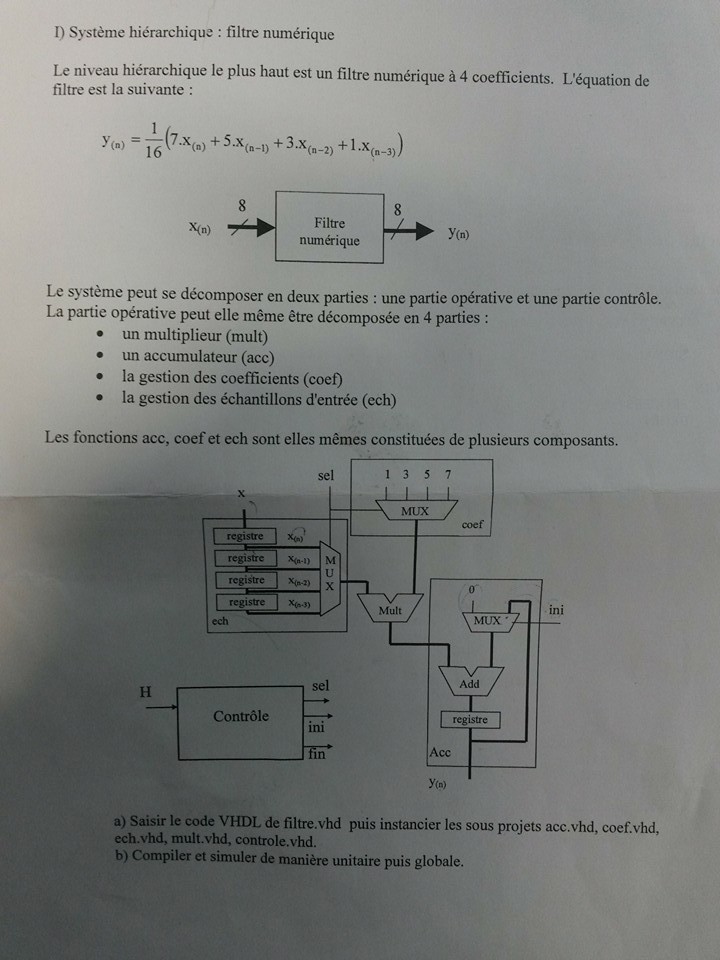

je suis étudiant en électronique et c'est la première fois que je travaille sur le langage VHDL j'ai vraiment besoin d'aide pour résoudre mon problème qui consiste a réaliser un filtre, lénoncé de l'exo est figuré dans la photo ci joint et merci d'avance

-----