Bonjour à tous,

Tout d'abord, c'est la première fois que je crée un sujet sur ce type de forum. Donc n'hésitez pas à m'avertir si mon post n'est pas correct.

Je viens de commencer un semestre d'étude au Danemark et je me suis malheureusement retrouvé dans un cours où certaine question ne sont pas de mon niveau ...

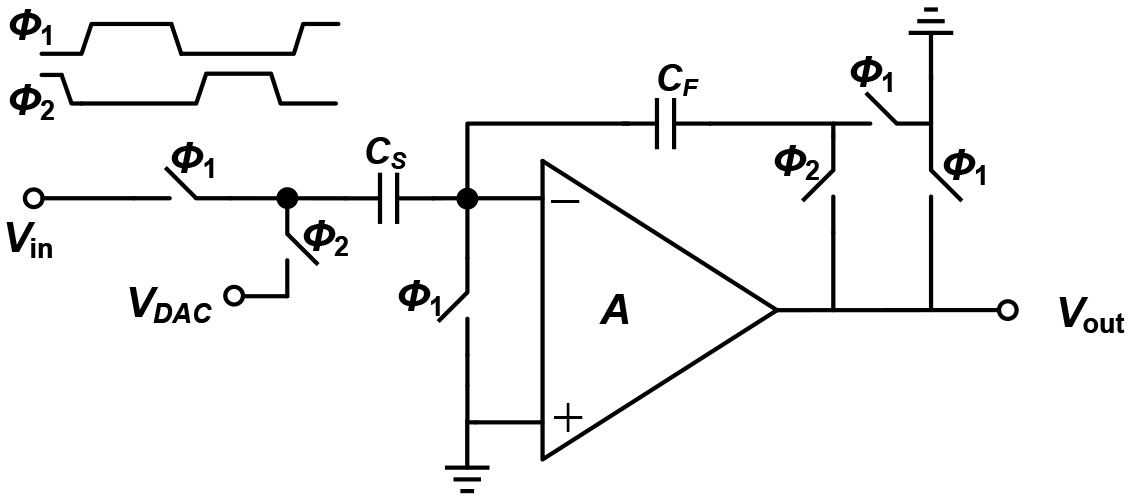

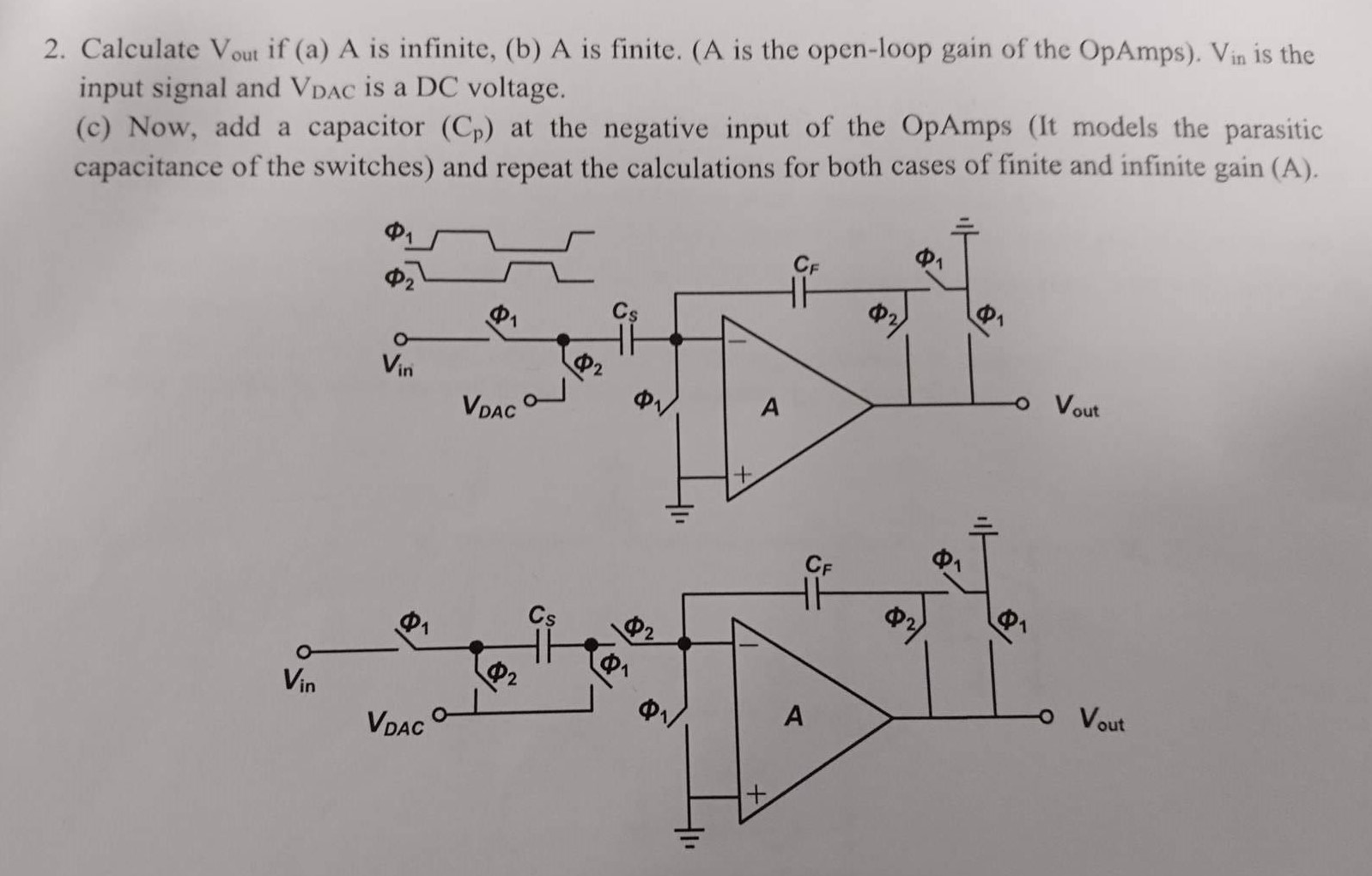

Je dois calculer la tension de sortie Vout dans le cas où le gain A de l'amplificateur serait fini et infini.

Mon problème se porte simplement sur des calculs d'électricité.

Dans le cas où le gain est infini (et donc où les tensions au bornes de l'amplificateur sont V+ = V-), je ne suis pas certain de l'exactitude de mes calculs.

Et dans le cas où le gain serait fini, je ne sais pas comment faire participer le gain dans mes calculs.

Pouvez donc m'aider à vérifier mes calculs et m'indiquer comment prendre en compte le gain ?

Cas du gain infini :

Je calcule la somme des charges du circuit.

Phi2 ON : On a Q2 = (Vdac - V-)*Cs + (Vout-V-)*Cf

Avec V- = 0 (relié à la masse) --> Q2 = Vdac*Cs + Vout*Cf

Phi2 ON et Phi1 ON : Q12 = (Vin+Vdac - V-)*Cs + (0 - V)*Cf

Avec V = Cs*(Vin+Vdac)/Cs+Cf (Point entre les deux condensateurs)

Et V- = 0

--> Q12 = (Vin+Vdac)*Cs - V*Cf

Et donc : Q2=Q12 <--> Vout = ((Vin + 2*Vdac)*Cs/Cf) - V

Est-ce correct ?

Cas du gain fini :

Ce que je ne comprends pas est que l'amplificateur est toujours relié à la masse.

Donc V+ = V- = 0 dans tous les cas.

Quel importance à donc le gain ici ?

Merci de votre aide,

Bonne journée,

Florian

-----