Bonjour,

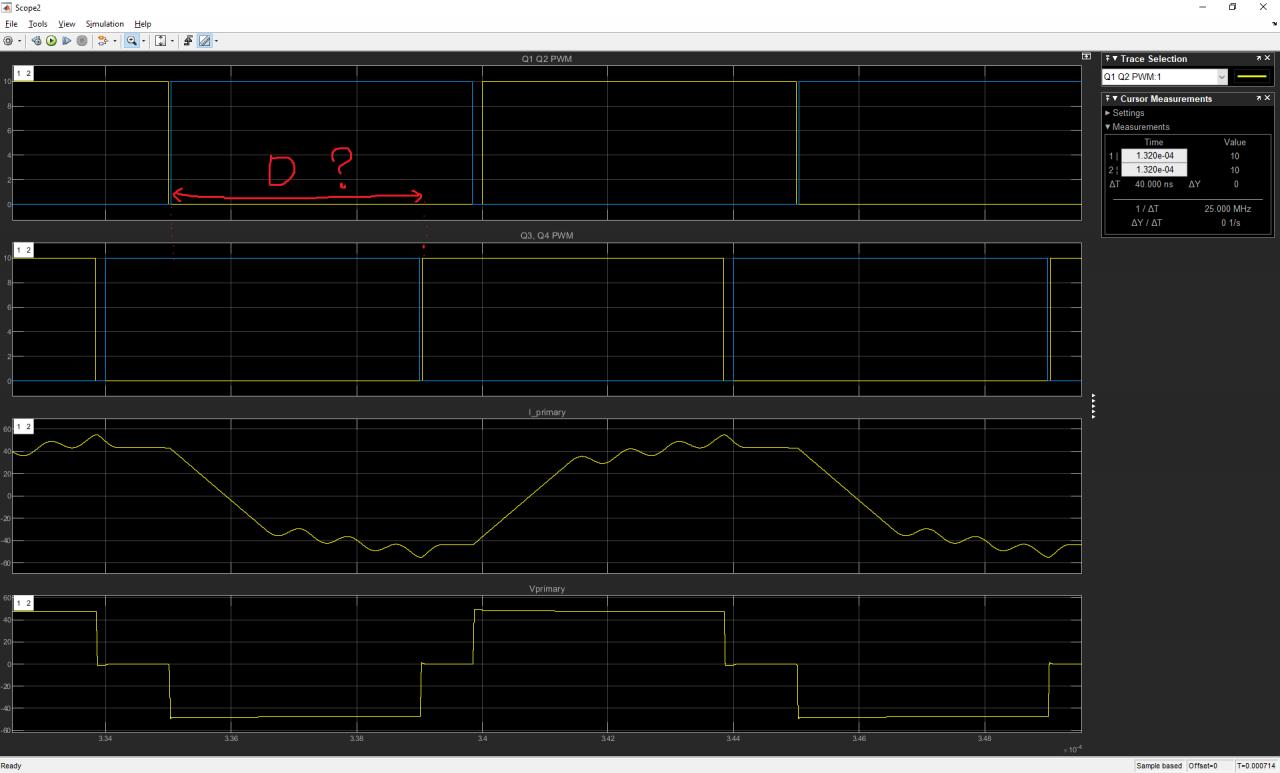

Après une longue pause sur le sujet, je reviens à la charge avec mon pont complet ZVS. L'objectif est de concevoir un étage boost isolé de 1kW (qui sera suivit d'un étage DC/AC) avec une structure Full Bridge Phase Shift converter. Je pars avec une tension d'entrée variant entre 40 et 60V et une tension de sortie de 350V. A pleine charge, il faut donc compter 30Arms côté primaire. Le transfo aurait un rapport de transformation Np/Ns de 12

J'ai bien compris que pour faire du ZVS, la première condition est qu'il faut que l'énergie stockée dans l'inductance parasite du transfo (+ éventuellement une inductance externe ajoutée volontairement) soit supérieure à l'énergie stockée dans la capa parasite équivalente (composée de deux capa Coss des MOS + la capa parasite du transfo) :

Ce qui revient à devoir respecter la condition suivante :

Le problème est que j'aboutis à devoir éventuellement fabriquer un transfo avec une cinquantaine de nH d'inductance de fuite. Ce qui me parait pas raisonnable du tout. Je fais appel à vous pour savoir si jusqu'ici mon raisonnement était correcte, et si oui comment gérer ce problème.

Quels seraient les conséquence d'une inductance de fuite plus importante que nécessaire ?

Voici un document de Texas qui explique grossièrement la démarche d'un tel dimensionnement :

http://www.ti.com/lit/ds/symlink/ucc...=1588841478945, à partir de la page 41

Mais je partirais plutôt sur un contrôleur avec drivers intégrés comme LM5046

Je vous remercie d'avance pour votre aide

-----

Je sais que ce n'est pas les connaissances qui vous manquent

Je sais que ce n'est pas les connaissances qui vous manquent