Bonjour,

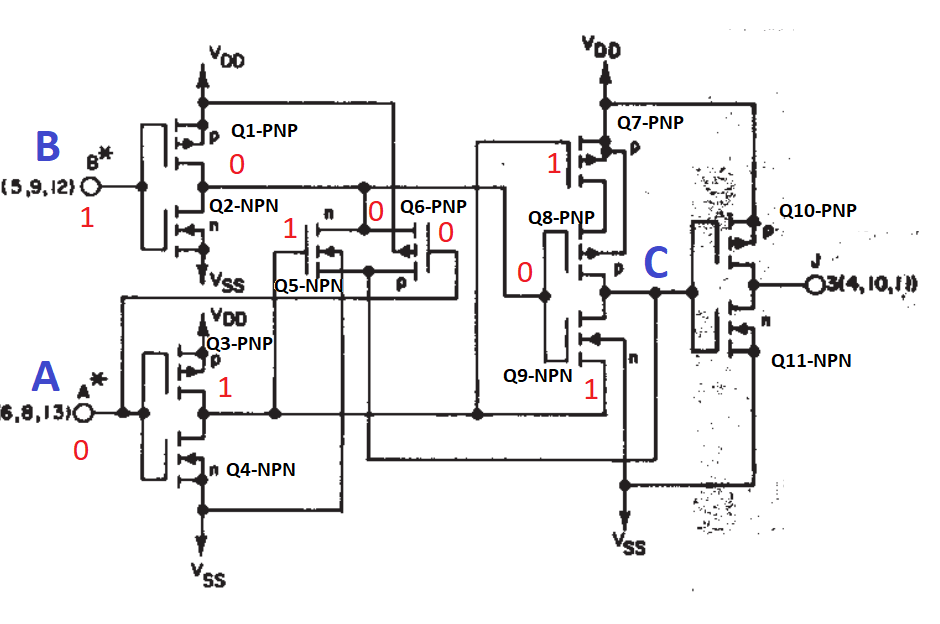

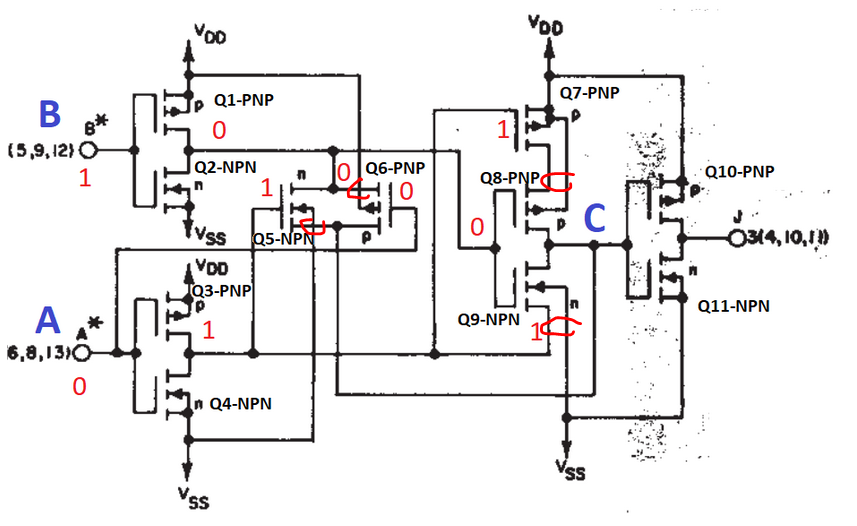

En observent la connectique interne du CD4030, pour le cas :

A = 0; B = 1, je ne comprends pas comment sont polarisées les grilles du totem pôle de sortie au point C.

Vu qu'on a affaire à un XOR, et que les deux entrées sont dans un état différent, on doit avoir la sortie à 1, et donc, 0 au point C, car le dernier totem pôle se comporte comme un inverseur.

Mais je ne vois pas comment avoir 0 au point C.

Pour moi, ce point est sous haute impédance car il est uniquement en contact avec des transistors bloqués :

Pour Q9 :

Le 0 sur l'entrée A, à travers Q3, Q4 amène un 1 sur sa source.

Le 1 sur l'entrée B, à travers Q1, Q2 amène un 0 sur sa grille.

VGS de Q9 est donc polarisé en inverse et vaut : moins VDD, Q9 bloqué.

Pour Q7 :

Le 0 sur l'entrée A, à travers Q3, Q4 amène un 1 sur sa grille.

VDD directement connecté sur sa source.

VGS de Q7 vaut 0V, bloqué.

Q7, Q8, Q9 ne permettent donc pas de fixer l'état de C.

Restent Q5, Q6 directement connectés à C.

Pour Q6 :

Sa grille est à 0 car directement connectée avec l'entrée A.

Sa source est à 0 via l'entrée B, inversée par Q1, Q2.

VGS de Q6 vaut 0V, bloqué.

Pour Q5 :

Sa grille est à 1 via l'entrée A, inversée par Q3, Q4.

Sa source est connectée au point C, lui-même à un état non défini car se trouvant entre Q7 et Q9 qui sont bloqués.

Je vois aussi que les substrats ne sont pas tous connectés à la source des transistors. Es-ce que cela change quelque chose ?

Mais surtout, la question la plus importante :

Sur un XOR : 0 et 1 en entrée donnent 1 en sortie, c'est à dire 0 au point C.

Comment le point C peut-il se retrouver à 0 dans ces conditions ?

Merci

-----