Bonjour à toutes et à tous.

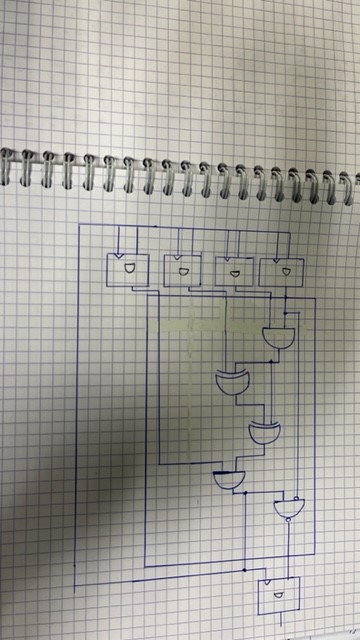

J'ai une petite question à vous poser. Admettons que j'ai en entrée d'un circuit logique une information qui doit être traité par ce circuit. Admettons qu'une nouvelle information entre dans ce circuit toute les 100 ns (soit avec une fréquence de 10MHz). Nous voulons maintenant que ce circuit traite une information toutes les 50 ns et non pas 100, soit une fréquence qui est doublée. Comment cela est t'il concrètement réalisable en utilisant la notion de pipeline ? Je dois aussi mettre sous forme de schéma cette solution. Je vous remercie de votre réponse, je continue de me creuser les méninges ....

Bonne fin d'après-midi.

-----

) causer dans le vide durant des jours

) causer dans le vide durant des jours