Bonjour à tous,

je tentais de réaliser un bloc en vhdl qui prend simple chaque valeur de 2 vecteurs et effectue un "et" logique entre eux, le tout dans un vecteur également.

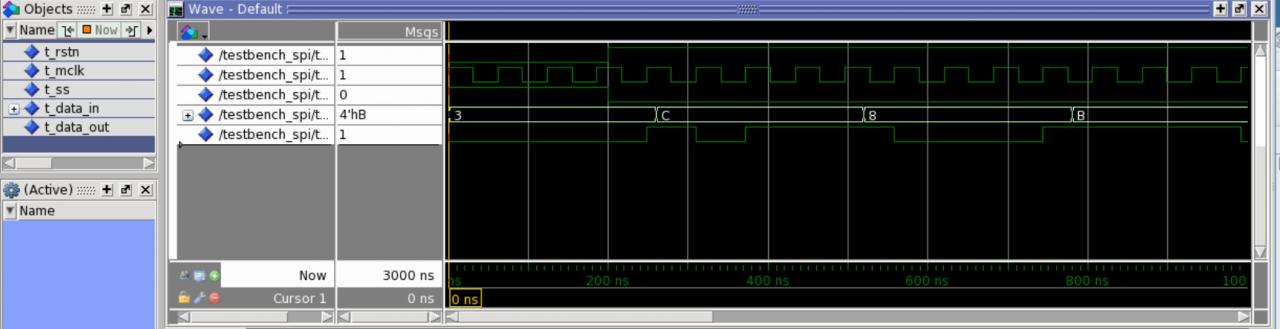

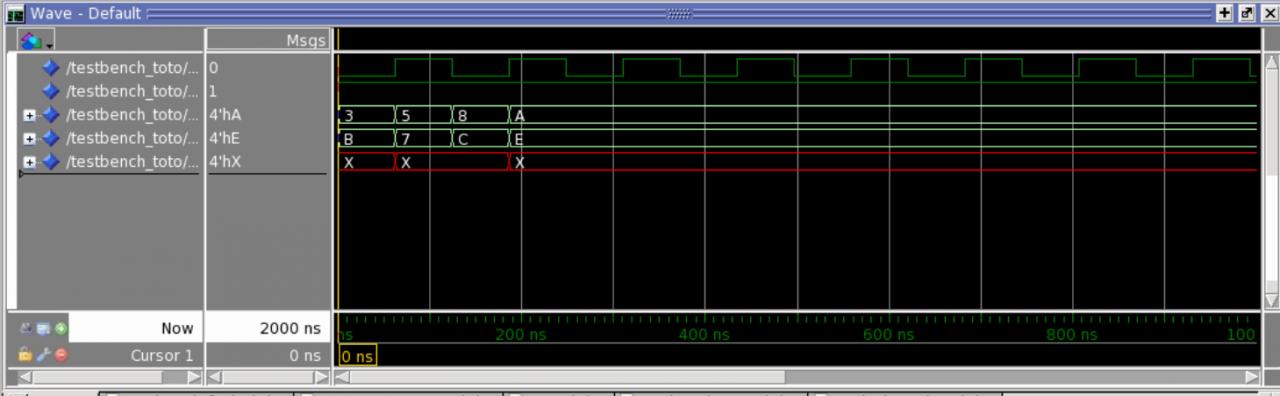

Pourtant, lorsque je simule la sortie est inconnue.

Voilà le code VHDL

Et voilà le code du testbench :Code:library IEEE; library work; use IEEE.STD_LOGIC_1164.all; use IEEE.numeric_std.all; use work.type_package.all; use work.func_package.all; use work.all; Entity toto is port( CLK : in std_logic; RESET_N : in std_logic; A : in std_logic_vector(3 downto 0); B : in std_logic_vector(3 downto 0); C : out std_logic_vector(3 downto 0) ); end entity; Architecture RTL of toto is --Signal signal data_out : std_logic_vector(3 downto 0); begin process(CLK) begin if(RESET_N = '0') then data_out <= (others =>'0'); elsif(rising_edge(CLK)) then data_out(2) <= A(2) and B(2); data_out(1) <= A(1) and B(1); data_out(1) <= A(1) and B(1); end if; end process; C <= data_out; end architecture;

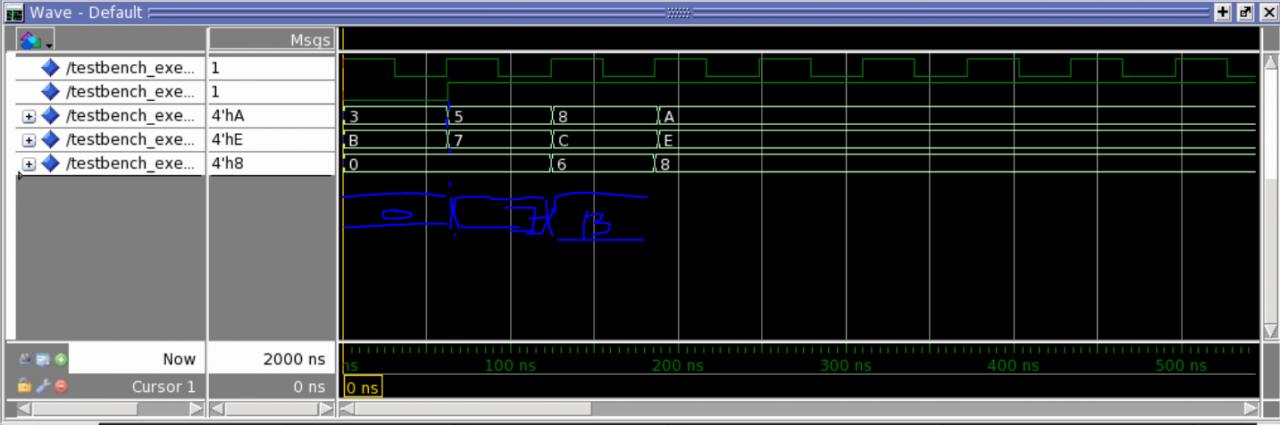

Cependant je n'obtiens pas le comportement souhaité et je ne sais pas du tout d'où vient le problème.[Code:library IEEE; library work; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use work.all; Entity testbench_toto is end entity; Architecture TB of testbench_toto is --Signaux signal t_clk, t_rstn : std_logic; signal t_a, t_b, t_c : std_logic_vector(3 downto 0); begin U1 : entity toto(RTL) port map(t_clk, t_rstn, t_a, t_b, t_c); process begin t_clk <= '0'; wait for 62 ns; t_clk <= '1'; wait for 62 ns; end process; t_rstn <= '1'; t_a <= "0011", "0101" after 62 ns, "1000" after 124 ns, "1010" after 186 ns; t_b <= "1011", "0111" after 62 ns, "1100" after 124 ns, "1110" after 186 ns; end architecture;

-----