bonjour,

vu qu'une diode led n'est pas un element Lineaire ( seuil led)

une resistance de charge (aux bornes de R+led) peut ameliorer la commutation.

-----

bonjour,

vu qu'une diode led n'est pas un element Lineaire ( seuil led)

une resistance de charge (aux bornes de R+led) peut ameliorer la commutation.

Il n'y a pas de dispute à avoir en technologie, seuls les arguments sont supérieurs ou inférieurs selon le contexte d'emploi.

Bien sur que le bipolaire peut satisfaire cette petite application, juste que le MOS est plus pertinent dans la majorité des applications aujourd'hui, quand il est utilisé et choisi à bon escient.

Pourquoi mettre un MOS de cette puissance? Pourquoi ne pas mettre un bipolaire en TO3 dans ce cas?

Un composant se doit d'être correctement dimensionné, comme tout en électronique qui est une science exacte.

Bonjour,

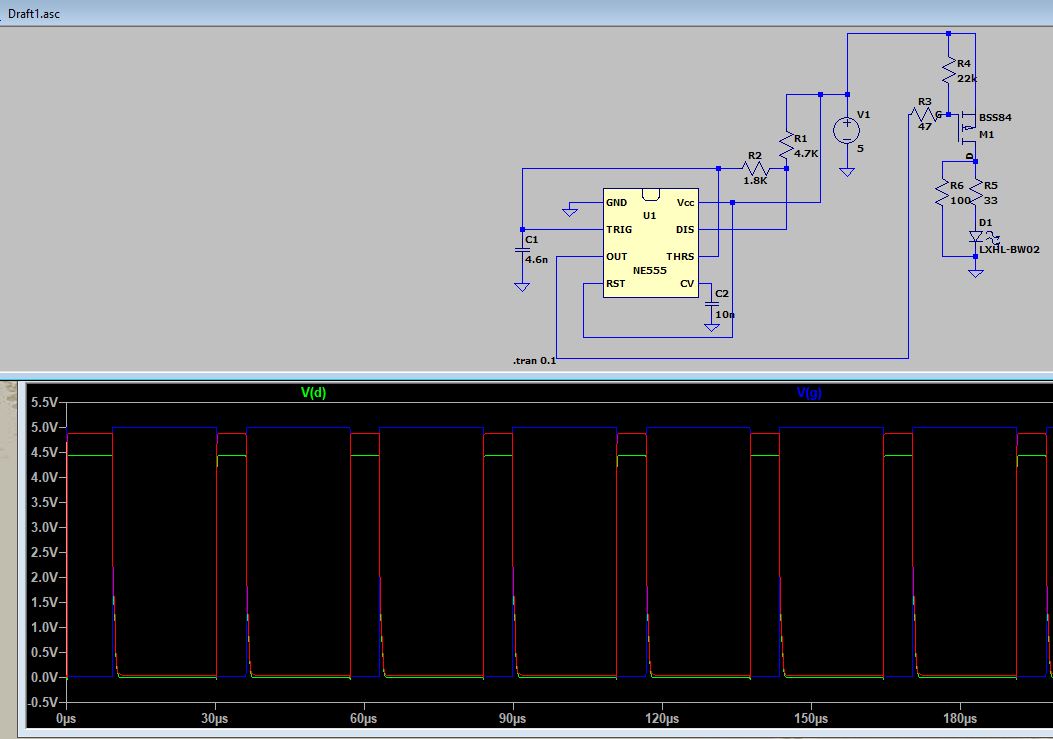

Oups, autant pour moi, il s'agit pas de mS mais de µS ...

Dans les télécommande du commerce, la base de temps n'est pas assuré par un simple montage RC, mais par un Quartz, de façon a garantir une certaine précision dans la fréquence d'émission de la DEL, donc, ici, en pratique, il faut soit utilisé des composant de précision (surtout pour le condensateur) ou prévoir une méthode d'ajustement de la fréquence (par utilisation d'un potentiomètre par exemple ...)

Cette résistance de tirage sert à fixer l'état de la gate pendant le démarrage du système, c'est à dire lorsque le signal en amont de la gate est en circuit ouvertIci jamdmnt a mis une pullup à juste titre car il utilise un P-MOSFET.

Ce problème m'intrigue , si on regarde en direct :

- Total Gate Charge = 9.5nC, en envoyant 5V cela revient à avoir une gate équivalente à une capa de 2nF environ.

- Le courant d'appel "instantané" d'une telle capa est = 2nF * (5V / tr,tf_555) soit 600mA sachant que tr,tf_555 est de 15ns typique. La résistance de protection de 47Ω, qui permet de limiter le courant sortant du 555 à une 100aine de mA est, justifiée et colle presque au 100mA max du tableau Absolute Maximum rating du 555.

- Toutefois cette résistance de gate a un impact sur le temps d'ouverture/fermeture du transistor puisqu'on a créé un circuit RC avec la capacité d'entrée. On sera un peu plus long a charger la gate mais aussi à décharger la capacité drain/gate. C'est pour cette raison qu'il existe des composants dédiés au pilotage des MOSFET capable de balancer un fort courant dans la grille mais aussi à pouvoir l'absorber lors de l'ouverture du MOS

- Le courant moyen appelé par la gate est fonction de la fréquence du signal du 555. A une fréquence de 40kHz la gate a une impédance de 1/(2*Pi*40kHz*2nF) = 2kΩ et appel donc un courant de 2.5mA sous 5V.

Le dimensionnement semble ok sauf que le simulateur montre une difficulté à décharger la charge (des capas parasites) accumulée dans le MOSFET. On a peut être un problème a évaquer Cgd (Crss) ?

Peut être une capa en parallèle de la pullup de 22kΩ pour offrir un circuit de décharge qui passerait par autre part que la résistance de grille ?

Là où il n'y a pas de solution, il n'y a pas de problème.

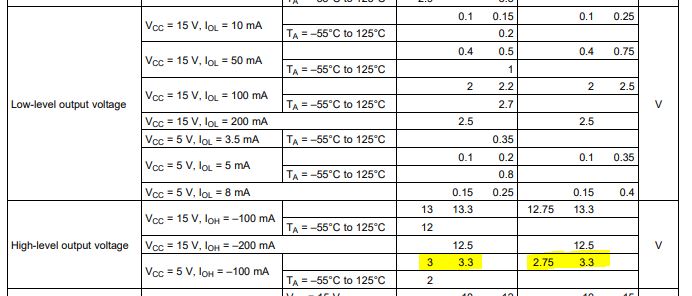

La doc spécifie la capa de grille à 510pF nominal, mais ici la tension d'alimentation du 555 est à 5V ce qui est sa limite de fonctionnement (4.5V), la tension de sortie sera au mieux de 3V à l'état haut si j'en crois la doc, donc insuffisant pour piloter ce type de MOS à l'ouverture efficacement, c'est à dire pour décharger suffisamment vite la capa d'entrée qui va maintenir un résidu de charge suffisant pour mal se bloquer.

Dernière modification par Antoane ; 18/02/2020 à 10h00. Motif: suppression PJ en double

Il faudrait baisser à 1K~2.2K la résistance grille-source.

Si jamdmnt peux faire la simu avec cette valeur on devrait voir une amélioration.

Sinon il faut changer le MOS pour une capa de grille bien plus faible, ou par un 555 Cmos qui lui n'a pas ce problème de niveau de rail d'alim aussi prononcé.

Arfff... oui tu as raison c'est Ciss qu'il vaut mieux prendre dans les calculs car si je pends QTotal Gate Charge de la doc, c'est que je me considère dans les conditions de test de la doc, incluant le VGS utilisé. La marge de sécurité devient trop grande.Envoyé par HULK28

La doc spécifie la capa de grille à 510pF nominal

Qg prend bien en compte les conditions de test

https://www.vishay.com/docs/73217/an608a.pdf

Là où il n'y a pas de solution, il n'y a pas de problème.

Re,

Comme suggère Vincent, j'ai testé avec une capa (10n à 100n) en // sur la R pullup (R4), bof, avec 100n, le signal est déformé, et avec moins, pas d'amélioration.

Dans le simu, du moins la version de 2017, il n'y a pas de 555 Cmos, donc pas de test possible.

En mettant un condo de 5,1nF au lieu de 4,7, on est à 38kHz, à quelques dizaines de Hz près. Et avec R2 de 1,2k au lieu de 1,8k, le signal est de ~5µs, et donc on peut augmenter le courant en diminuant R3, avec 22 ohms on a ~140mA.

Même si le signal n'est pas très "carré", comme il n'est pas émis très longtemps, je ne pense pas que la diode souffrira.

Il y a aussi la capacité de sortie du MOS qui est ici très faible mais qui va se décharger très lentement avec le courant de fuite.

C'est pour cela qu'il vaut mieux bien choisir son MOS.

Pour limiter son effet il faut reprendre l'idée de paulfjujo au #31 et ajouter une résistance de tirage en parallèle du circuit led, une 220 ohms devrait suffire pour que tout rentre dans l'ordre avec ce modèle de MOS.

A mettre aux bornes de la résistance et de la led.

Comme j'ai mis du temps à taper mon message, je n'avais pas vu les derniers de Hulk et Vincent.

J'ai testé avec R Pullup de 1 et 2k2, pas de changement.

Mais les simu sont loin d'être parfaites. Le même montage avec Multisim ne donne pas la même forme de signal, voir schéma joint.

Ok alors ce n'est pas un problème d'évacuation de la charge mais HULK28 met en avant la possibilité que la tension de sortie du 555 ne soit pas suffisante pour bien piloter le MOS (mauvais pilotage donc mauvais résultat)

En gardant tel quel ce schéma tu peux augmenter la tension d'alimentation générale à 15V, d'après la doc le 555 on peut aller jusque là. Ça va augmenter la dynamique du VGS.

Là où il n'y a pas de solution, il n'y a pas de problème.

Voici avec LTSpice et la modif dont j'ai parlé.

Dernière modification par Antoane ; 18/02/2020 à 09h59. Motif: suppression PJ en double

Une autre simulation qui montre cette fois la conduction molle d'un gros MOS et sans la résistance de tirage en sortie:

influence_MOS.JPG

Même montage avec cette fois la résistance de tirage:

avec_résistance de tirage.JPG

Dernière modification par Antoane ; 18/02/2020 à 09h59. Motif: suppression PJ en double

Les signaux avec les 2 simus.

Bonne soirée.

Bonjour,

Je n'ai rien contre un montage avec FET, cependant, si tu as des 2N2222A sous la main, il n'y a aucune raison de ne pas y arriver avec ce type de transistor.

En partant du schéma donné message 3 :

La caractéristique donnée de Vsat à 150 mA n'est pas la plus adéquate pour évaluer le HFE, on y lit simplement le rapport IC/IB utilisé pour la mesure de VCE sat.

On dispose de la caractéristique plus adéquate "DC Current Gain", on y lit que pour VCE = 1 V et Ic = 150 mA, on a HFE > 50.

Donc, on est sûr qu'en calculant avec HFE = 50, la tension VCE sera < 1 V (avec Ic = 150 mA ... et 100 ma également d'ailleurs)

Si on désire Ic = 100 mA, un Ib = 2 mA devrait suffire (et Ib = 3 mA donne un coefficient important de sécurité).

En tenant compte de la chute de tension dans la diode (environ 1,5 V) et de la tension VCE < 1 V avec VCC = 5V, il faut Rc = (5 - 1,5 - 1)/0,1 = 25 ohms (mettre par exemple 22 ohms 0,5 W)

Il vaut mieux ajouter une résistance entre la base et l'émetteur du 2N2222A car la tension de déchet niveau bas du 555 pourrait être proche de 0,6 V (si alimenté en 5V) et cela pourrait ne pas bloquer correctement le 2N2222A.

Compte tenu de cela et avec V out haut 555 = 4,4 V (min), une résistance de 1 kohm entre la sortie du555 et la base du 2N2222A est OK ... et on met aussi une résistance de 1 kohm entre la base et l'émetteur du 2N2222A

Et cela devrait être bon... à condition évidemment de monter le 2N2222A dans le bon sens (voir message 15)

Bonjour,

Black Jack, tu fais comme beaucoup, tu confonds HFE en amplification et celui en saturation, vois le #7 et/ou la datasheet.

D'autre part, un NPN n'est pas le plus adapté, car avec le signal en sortie du 555, le led est éclairée trop longtemps.

Avec un 2N2907 que j'ai mis en #26 la led n'est éclairée que ~20% du cycle et le courant plus élevé.

Comme on l'a dit un PMos est bien plus performant. Celui que j'ai mis, irlml5203 est à 36cts chez Radiospares, et le port est gratuit si l'on commande le week end.

Salut jamdmnt,

Non. Pas du tout."Black Jack, tu fais comme beaucoup, tu confonds HFE en amplification et celui en saturation"

Il y a Hfe qui est le gain en courant petit signal autour d'une valeur de Ic donnée et VCE donnée.

Il y a HFE pour le gain en DC pour un Ic donné et une VCE donnée.

Il y a le rapport Ic/Ib utilisé pour donner une valeur de VCE sat pour un Ic donné.

Ce dernier n'est pas représentatif du tout du gain en courant disponible près de la saturation.

Ici, on dispose d'un gain en courant > 50 pour Ic = 150 mA et VCE = 1 V, on n'est pas saturé mais cela n'a pas d'importance, on peut calculer avec ces valeurs dans le cas présent.

Si le transistor sature, on aura un poil plus de tension sur la LED, pas de soucis.

En général, pour les "petits" transistors, on mesure la VCEsat pour un rapport Ic/Ib = 10, c'est vrai pour quasi tous les "petits" transistors et ne représente pas du tout une image du gain en courant disponible dès que la tension est un quart de poil supérieure à la tension VCEsat donnée dans la datasheet.

Bonjour,

tu a raison Black Jack 2, mais perso, je préfère le montage proposé en #10, car il utilise le duty cyle dans le bon sens (la diode n'est alimenté que durant 20µS) et le courant de base s auto-adapte au gain du transistor ...

Dernière modification par DAT44 ; 17/02/2020 à 19h34.

bonsoir

avec un BJT en saturation il faut aussi penser à le désaturer, je dis çà je ne dis rien.

JR

l'électronique c'est pas du vaudou!

Bonsoir à tous,

Voilà énormément d'infos et je vous en remercie, mais si j'ose l'avouer tout ça m'a mis un peu dans le brouillard ! Sur la question faut-il prendre un Mos ou un bipolaire, j'imagine que vous avez beaucoup d'éléments de réponses mais je vais me mettre la contrainte d'utiliser uniquement des transistors bipolaire, je veux me familiariser un petit peu plus avec cette famille de composant.

Le schéma de jamdmnt au poste #18 me semble intéressent, (utilisation de PNP et NPN). Mais je reviens vers vous car je ne comprends pas cette résistance R6 de 10K au niveau de l'émetteur de transistor PNP. Esc-ce une résistance pull down ?

Je n'ai pas délaissé le projet ni la discussion mais je vous avoue que toutes ces infos m'ont un peu fait transpirerd'où un temps de réponses anormalement long.

Bonsoir,

Oui, il s'agit bien d'une résistance de pull down , pour dé-saturé Q1 (un peu faiblarde a mon gout, je la passerait bien a 2,2K, voir 1K ...)

Et d'après toi selon quel critère?

Il me semble que tu fais ça au pif...

Il y a pourtant dans la datasheet du transistor de quoi la dimensionner au mieux.

Bonjour,

On na pas besoin de 2 transistors pour "passer" du courant délivrable par le 555 à un courant de 100 mA dans la LED.

Et si on n'est pas satisfait des caractéristiques de désaturation, il existe de nombreuses possibilités pour les améliorer... par exemple empêcher le transistor de saturer, par l'utilisation de 1, ou mieux de 2 diodes schottky.

Voici par exemple pour un 2N2222A.

Plus économique, un condensateur en parallèle sur la 680 ohms.

En prenant C<1/(20*Rb*f)

Dans le schéma de Black Jack2 et à 40kHz ça donnerait 1.5nF.

Lorsque Vin est tiré à 0V le condensateur présente une brève tension négative sur la base, ce qui accélère la libération des charges.

Plus rigoureusement il faudrait splitter la 680 ohms en 2x330 ohms en série et mettre un 3.3nF sur une des 330 ohms.

Pauvre MatMacMat...

Après le montage Baker clamp de Black Jack 2, v'là que HULK28 te montre ce qu'est le montage speed-up capacitor

L'électronique ? Mais c'est facile

Là où il n'y a pas de solution, il n'y a pas de problème.

Ahahaha hahaha

^^ ahah ! mais je ne désespère pas = )

Je suis donc partie sur la méthode de jamdmnt. J'ai voulu faire par étape, donc j'ai essayé d'inverser le signal, j'ai donc mis en place le schéma post #18. Cela fonctionne (je n'en aurais pas douté) maintenant je cherche à comprendre, n'ayant PAS du tout l'habitude des transistors PNP je ne comprends pas le raisonnement. Pourquoi cette résistance R5 de 470 ? Ainsi que celle de R4. Je comprends leur rôle mais pas leur valeur, comment les déduirent ?J e n'arrive pas à faire la relation entre les deux transistors !

Ib du NPN doit-il être calculer à l'aide du VCE (sat?) du PNP ?

PS : Je ne retrouve pas les même valeurs que sur votre lien sur le timer 555 :http://www.ohmslawcalculator.com/555-astable-calculator. Et la sortie 555 est en dessous de seuil minimum de 4.4V. Dois je en déduire que mon circuit est dysfonctionnel ?

Malgré tous, toutes ces réponses me permettent de voir que pour un problème plusieurs solutions existent !

Bonjour,

le site donne une fréquence de 38Khz, et un temps d'éclairage de la DEL de 5,7µS.

C'est quoi ce seuil minimum de 4,4V ?