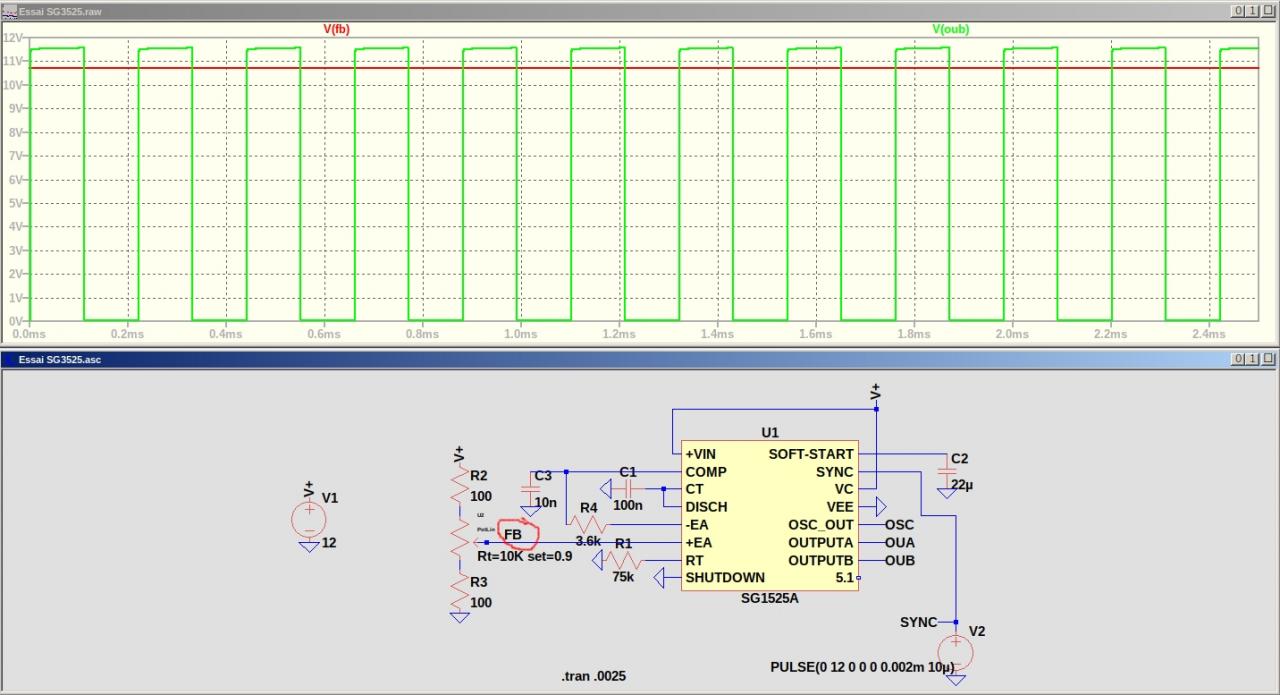

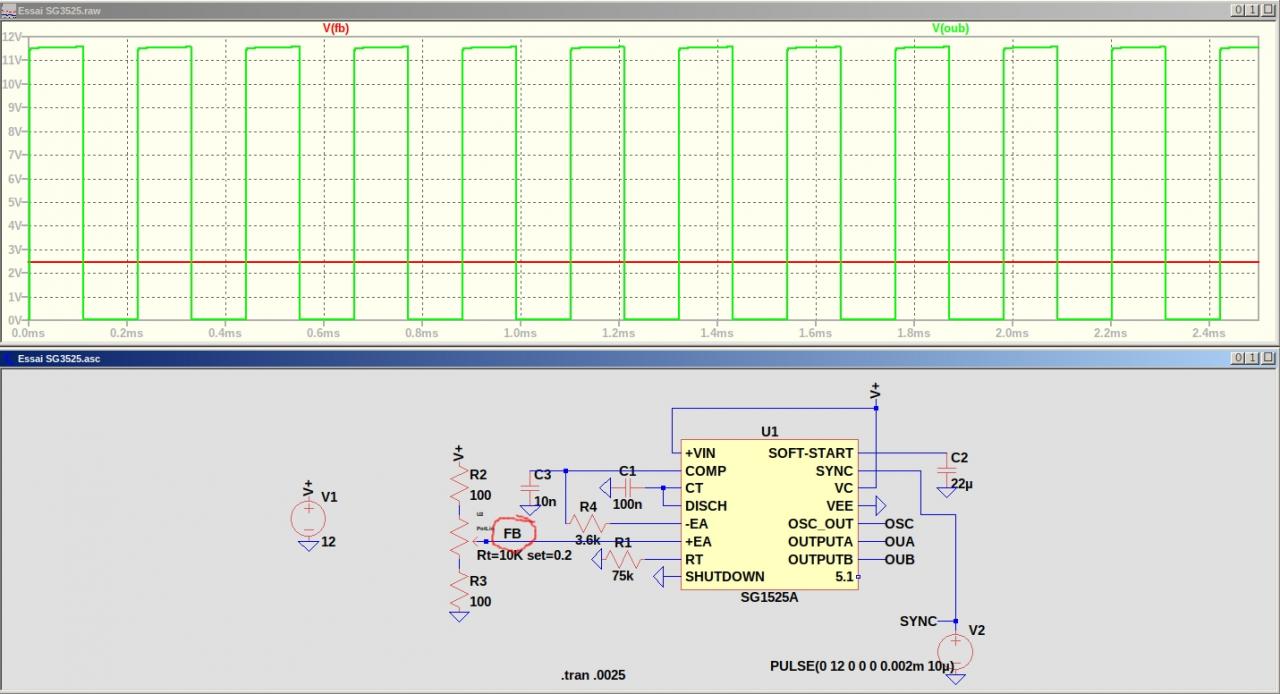

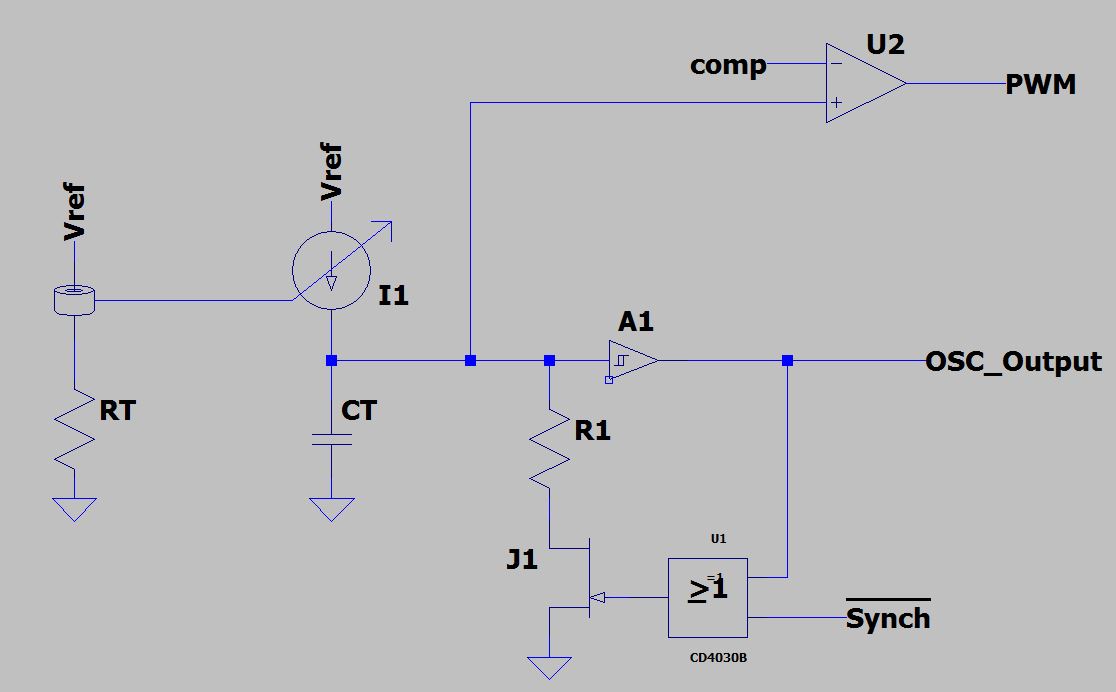

Bonjour tout le monde, je cherche a produire un signal de 100KHZ avec un 3525 PWM le souci est que je n ai pas de pwm avec signal exterieur! alors qu avec condensateur et resistance variable pin 5 et 6, la j ai du PWM de 0 a 49%!

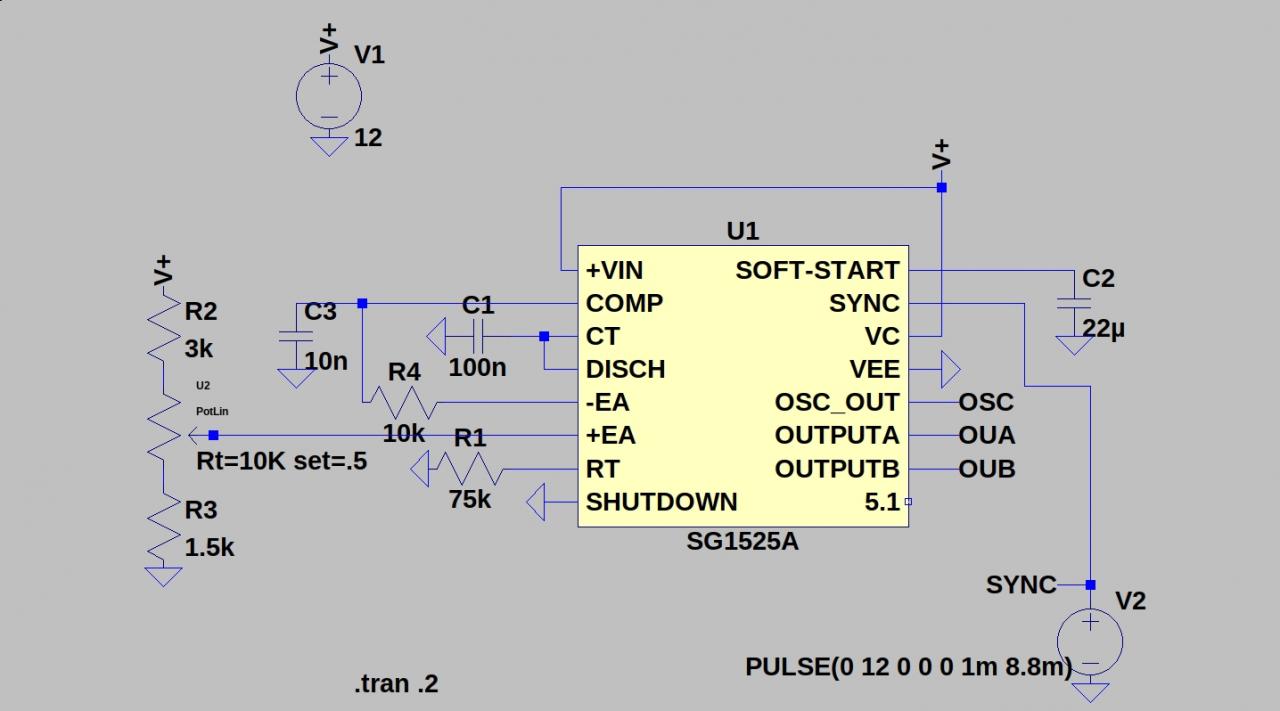

Je vous laisse mon schéma car je ne comprends pas l érreur!merci!

-----