Projet : génération d'horloge (issue d'une discussion sur le Forum électronique)

Le problème de base :

Voila j'ai acheté dernièrement une ancienne horloge de Gare de marque BRILLIE. Ces Horloges fonctionnaient avec une horloge mère qui envoyait des impulsions de polarité inversée toutes les 30 secondes à toutes les horloges secondaires ce qui permettait d'avoir exactement la même heure à toutes les horloges en même temps. Cependant n'ayant pas d'horloge mère, et n'étant pas intéressé pour en acquérir une (trop chère, et pas collectionneur) celle la me suffit, et j'aimerai la faire fonctionner.

http://forums.futura-sciences.com/sh...highlight=4060

Une solution

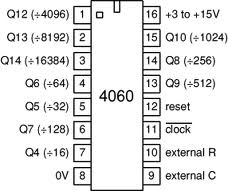

L'idée est d'utiliser un 4060 qui contient 14 diviseurs par deux et a la possibilité d'utiliser un quartz pour avoir une bonne stabilité. Le 4060 existe en deux technologies avec la même fonctionnalité pour notre application :

- CD4060 (alimentation Vdd = 5 à 15V) http://www.datasheetcatalog.net/data...0/CD4060.shtml

- 74HC4060 (alimentation Vdd = 2 à 6V) http://www.datasheetcatalog.com/data...74HC4060.shtml

Avec un quartz " horloger " de 32768 Hz, il est possible de générer des fréquences très basses ( 2 Hz). Hélas, c'est une fréquence encore trop élevée pour la pendule qui demande 1/60 Hz pour fonctionner. Donc, on utilise un deuxième 4060 pour obtenir la bonne fréquence. On pourrait utiliser un 4040 ou un 4020, mais c'est plus facile pour l'approvisionnement, d'utiliser le même composant. Le 2 Hz est donc divisé par le second 4060 par 128 et on obtient une fréquence de 1/64 Hz avec la stabilité du quartz. Comme c'est dommage, il fallait 1/60 Hz ! On reverra le problème plus tard.

Le signal de sortie du 4060 est en 0V/Vdd, mais on ne peut pas tirer beaucoup de courant, moins de un milliampère. Donc pour alimenter la bobine réceptrice, il faut :

- Augmenter le courant de sortie : Ceci est fait avec deux transistors NPN et PNP montés en suiveur (n'importe quel transistor est utilisable)

- Générer une impulsion négative et une impulsion positive : Un condensateur de 470µF en série avec une résistance de 22 ohms fait le travail (ces valeurs ont été déterminées expérimentalement et dépendent de la valeur de Vdd et de la sensibilité mécanique et électrique de l'horloge)

Il faut maintenant résoudre le problème du diviseur par 60 à la place de 64, sinon notre horloge retardera systématiquement.

Le compteur par 64 est composé de 6 bascules binaire et ce qu'il faut, c'est remettre le compteur à zéro quand il y a eu 60 impulsions (et non 64). La valeur de 60 (décimal) se code en binaire 111100

60 = 1*32 + 1*16 +1*8 + 1*4 + 0*2 + 0*1

Donc il faut détecter que les quatre bascules de poids forts sont dans l'état " 1 " et, dans ce cas, forcer une remise à "000000".

Ceci se fait facilement avec une porte AND à quatre entrées. En fait, on utilise une porte NAND de type CD4012 qui est plus facile à trouver, suivis de l'autre moitié du CD4012 montée en inverseur. Donc quand le compteur arrive à la valeur décimale 60 (111100 en binaire ou 0x3C en hexadécimal), la sortie du AND passe à l'état "1", qui est juste le niveau qu'il faut pour remettre le 4060 à zéro. Le seul (léger) inconvénient de ce montage, c'est que la sortie d'horloge à 1/60 Hz reste 32 secondes à l'état "0" et 28 secondes à l'état "1", mais cela ne présente aucun problème pour la précision de la minute.

La première image représente le schéma final

La deuxième image représente le chronogramme du compteur par 60

La troisième image représente une simulation (simulation MicroCap 9) des signaux envoyés à l'horloge

-----

qu'un PIC que l'on ne sait pas programmer

qu'un PIC que l'on ne sait pas programmer